We are using the output of the V1V8 SMPS switch outputs on a TWL6030B107CMR device as a reference voltage on a XILINX FPGA and PROM (XC6SLX45-2CSG324 and XCF16PFSG48C).

The issue we are facing is as follows:

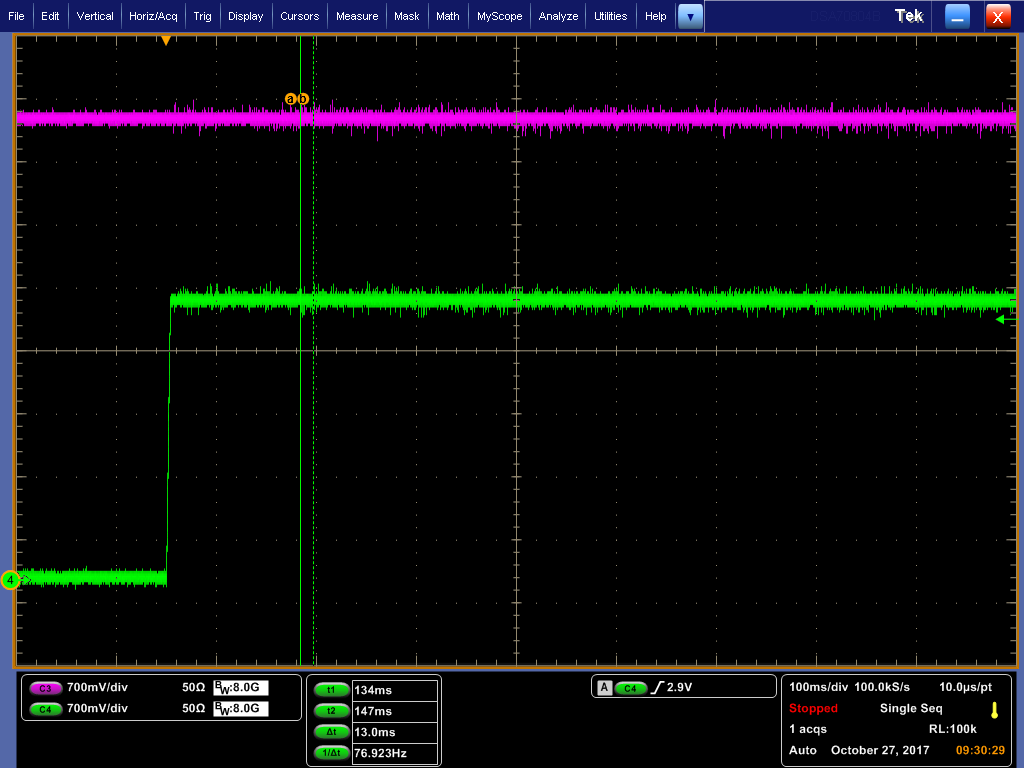

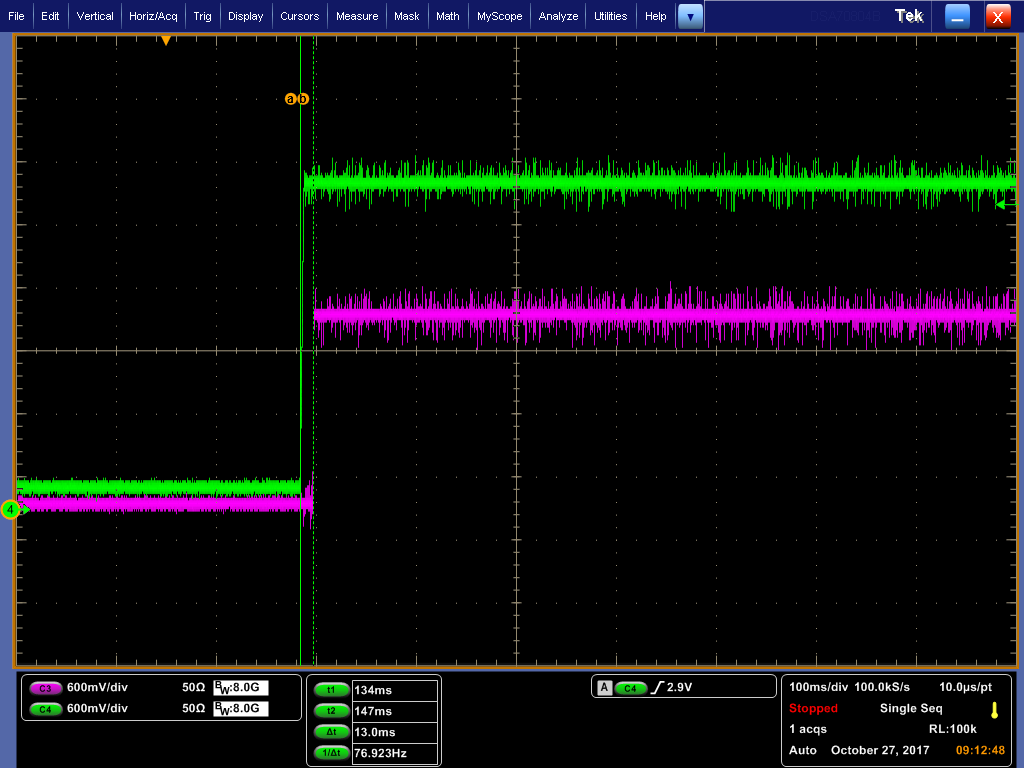

When booting our board with nothing connected to the VBUS inputs on the TWL6030, the V1V8 power rail comes up at our FPGA device (and PROM) on average 10-15ms after the 3.3V rail (Analog input voltage supply + VBAT) and the FPGA device loads and configures correctly from the PROM.

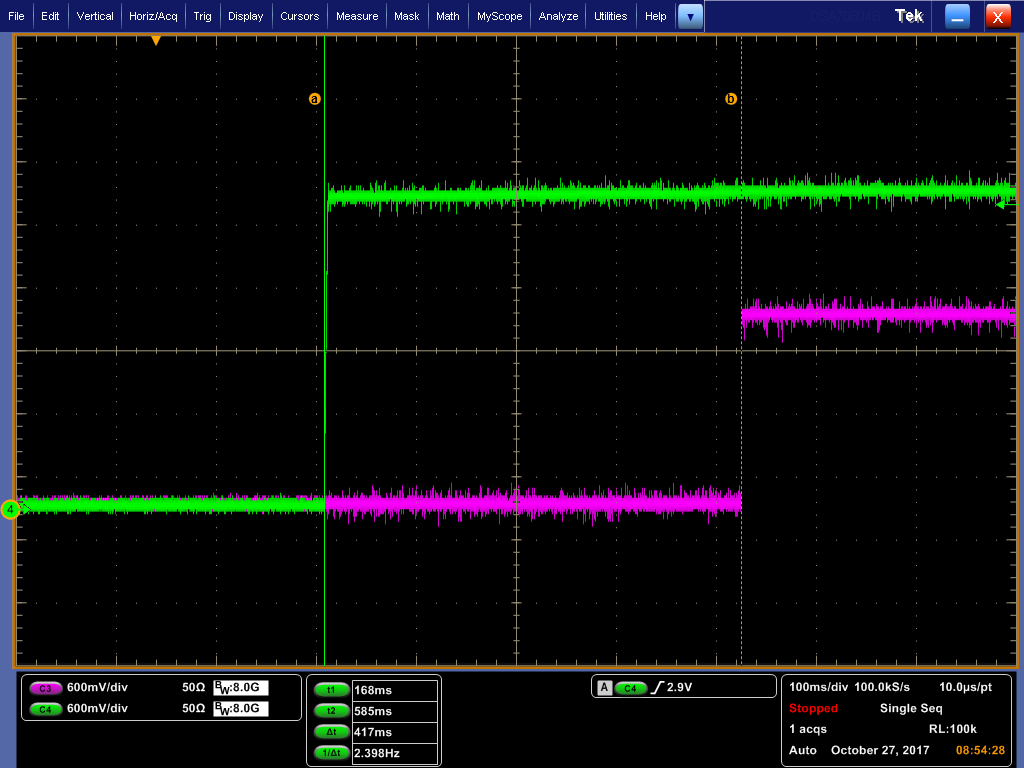

When booting our board with USB connected to the VBUS inputs on the TWL6030, the V1V8 power rail comes up 400-450ms after the 3.3V rail and causes the FPGA configuration to fail.

Plugging the USB device in after boot does not cause the issue (the FPGA is well programmed and running by then) but is not feasible for our usage.

Is there any known issue with TWL6030 that may be causing this behavior or any leads that I can try to hunt down the cause?