Other Parts Discussed in Thread: , BQ76PL455A-Q1

Hi everyone,

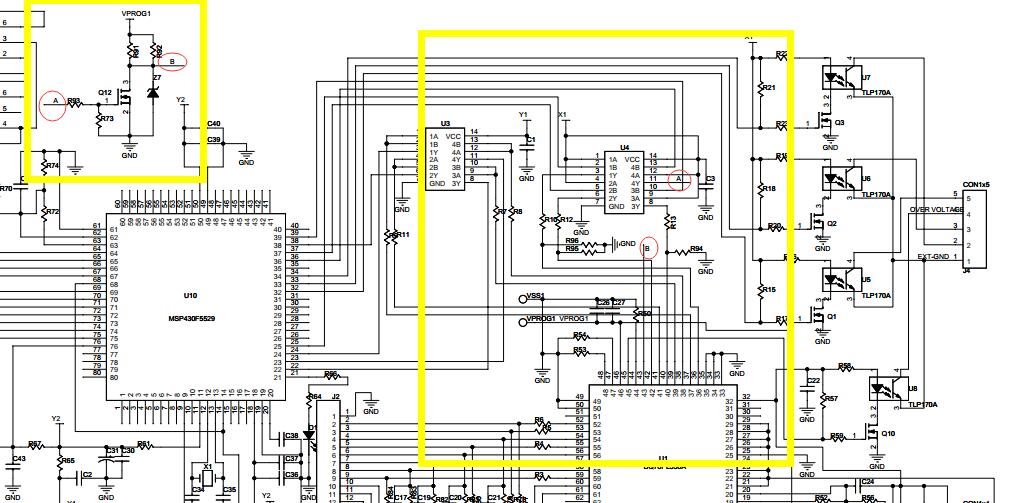

i am using three bq76pl536s in a bms project , my question is about the CS_H design of the bq on the bottom chain, i wonder if there problem on my SCH ;

i do as the follow :

http://www.ti.com/lit/ug/tidub04/tidub04.pdf page 15.

but ,the question is,when i set the resister between CS_H and LDOD is 1k; i found that the LDOD canot go up normally such that it keeps 0V ;

when i set the resister to 5.1k; and it works normally;

so i wonder which value of the resister is suitable or the sch itsself is wrong;

the othe question is ,in some product of this project ,some bq consumes high current after it goes to sleep a period of time ;it seems like the bq active itself after it went to sleep fo a period of time;