Hi team,

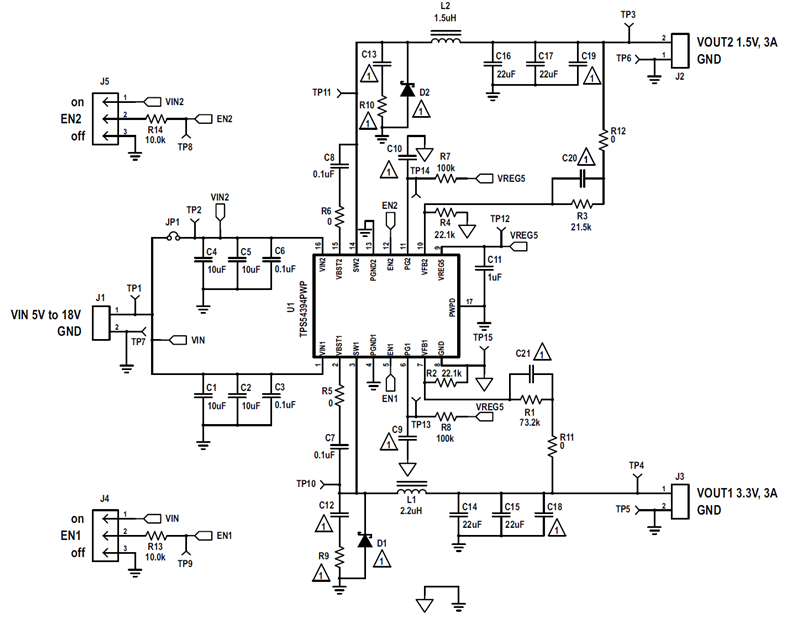

I have one question about the Power Good connection of TPS54394.

In our EVM, PG1, PG2 are pulled up through 100k resistor to VREG. I think this is because the PG1,PG2 max voltage is 5.7V. Is that right?

If my input voltage is 5.5V, can I pull up PG1, PG2 through 100k resistor to Vin(5.5V) directly?

Thanks,

Will