We are currently assembly a few hundred of system with BQ78PL114 + BQ76PL10. We have 5 cells in serie (typical voltage at assembly of 3.2V), so we have one slave and one master. All of our batteries have FW4452 (we designed when FW5000 was not released, so we cannot upgrade with our current PCBs)

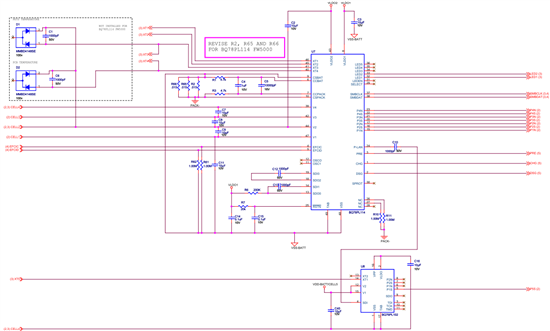

You will find at the end of this post picture of the schematics we have. They are very similar to the reference specs

The issue we're having is that after assembly, many (>25%) of the boards fails to operate correctly. The typical problem is that the slave is unresponsive. I can communicate with BQWizard but I get some garbages values (I can read and write in some fields such as "manufacturer", and it reads back correctly) but when it comes to reading voltages or temperature, all I get is the default 2000mv.

I've been able to somehow revive it by loading a 4 cells .aux files so that it ignores the 5th cell, and it works (all voltage and temperature can be read, except for the 5th cell)

The VLAN flag doesn't raise, but I can assume that the slave is broken and that it prevents the master from functionning correctly.

Moreover, on broken boards, the VLDO and VPP pin of the slave read 3.2v instead of 2.5V (3.2v being the voltage of the cell). It's like if the LDO blew up and outputs the cell voltage without regulating.

I've seen this also on some LDO on the master (VLDO1 and VLDO2). In that case, communication was not possible at all

I am taking extreme care of loading the cells in order, beginning with the lowest cell, then going up until the most positive cell is connected. But that doesn't seem to solve the problem.

I am also taking extreme care in regards to ESD. The circuit also have most ESD protections of the EVM.

Somehow these problems occurs out of the box, sometimes they just stop working after assembly for no reason while they were working fine before.

The chips seem very weakened; they were assembled by a professionnal assembly fab. I am starting to question the reflow soldering temperature, but since I cannot find any information in the datasheets

Did anyone experience such mysterious fails ? Anyone can explain why such high voltage is present on the LDO pin ?