Other Parts Discussed in Thread: LM76003, TPS54360, TPS54560, LMR16030

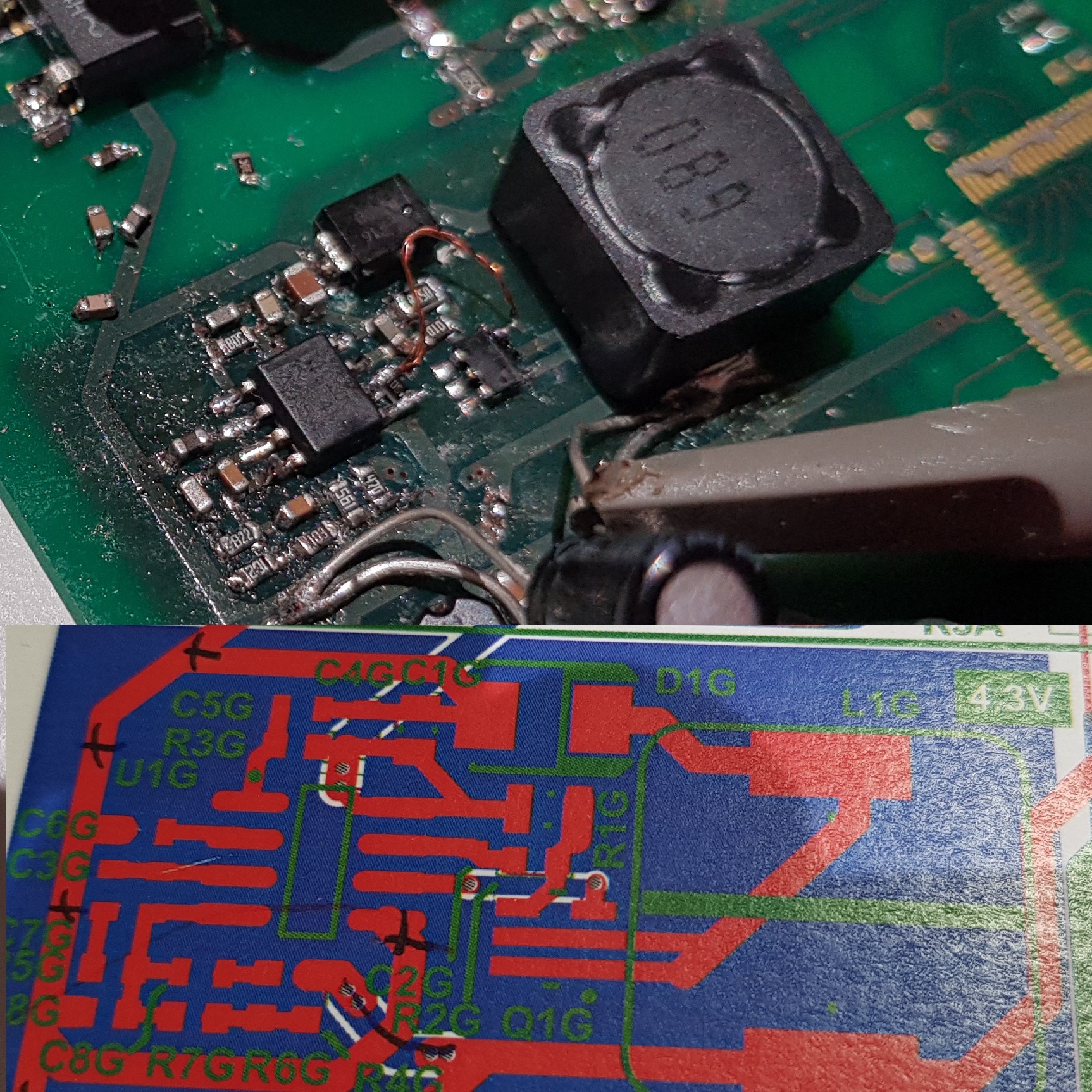

Hi, I'm using TPS40200 on my design and while all components arrive, I've using some similar parts (+- 20%) to test. I dont expect to work perfectly but a little bit. The problem is I can't achieve this.

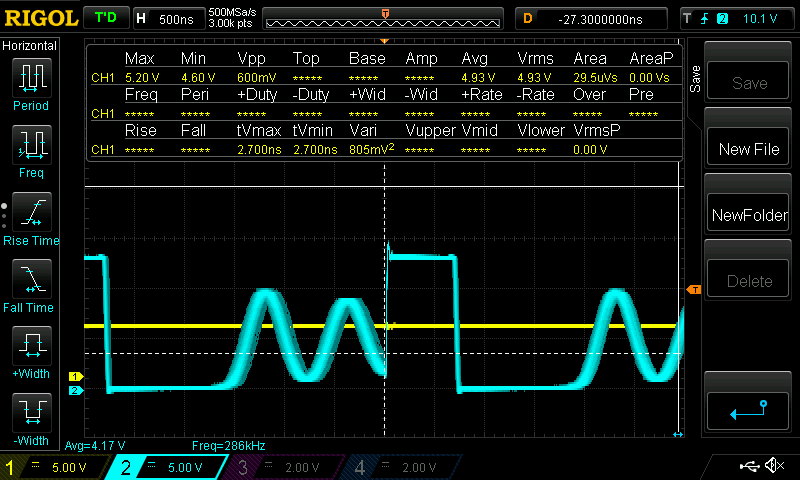

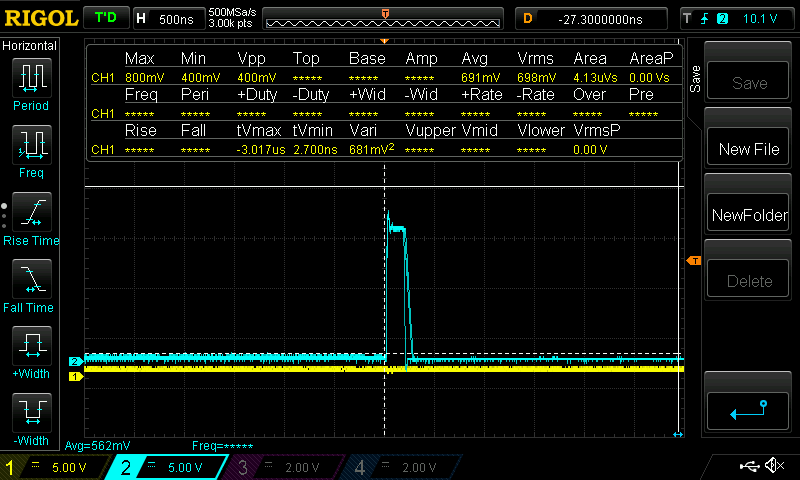

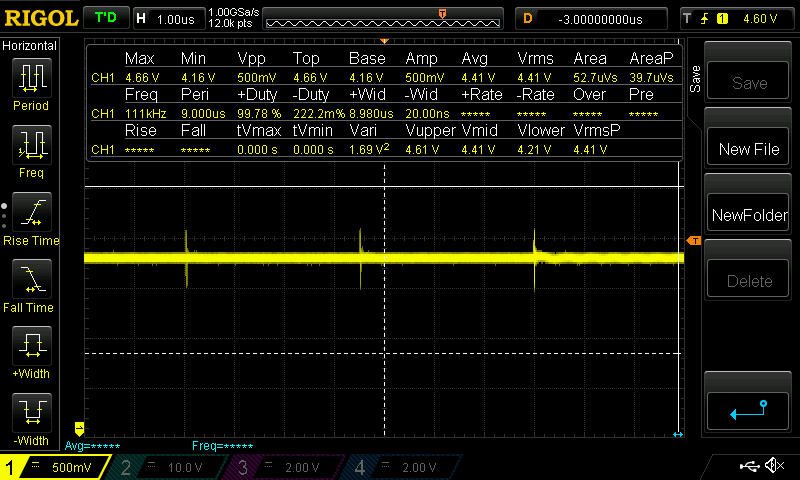

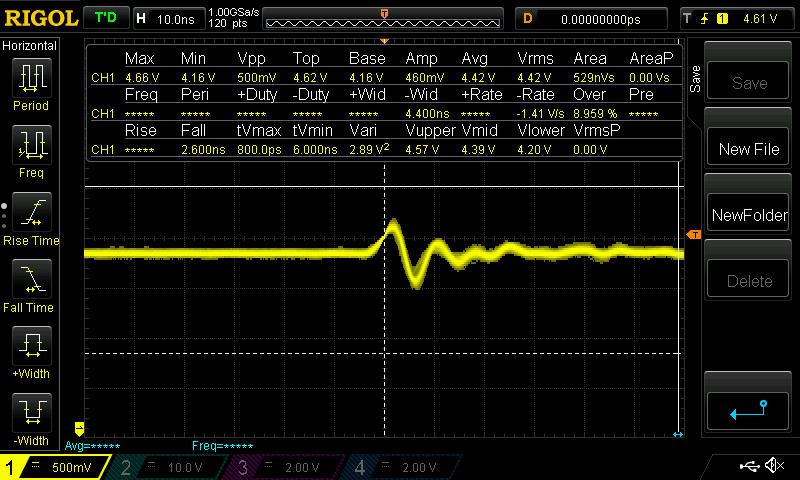

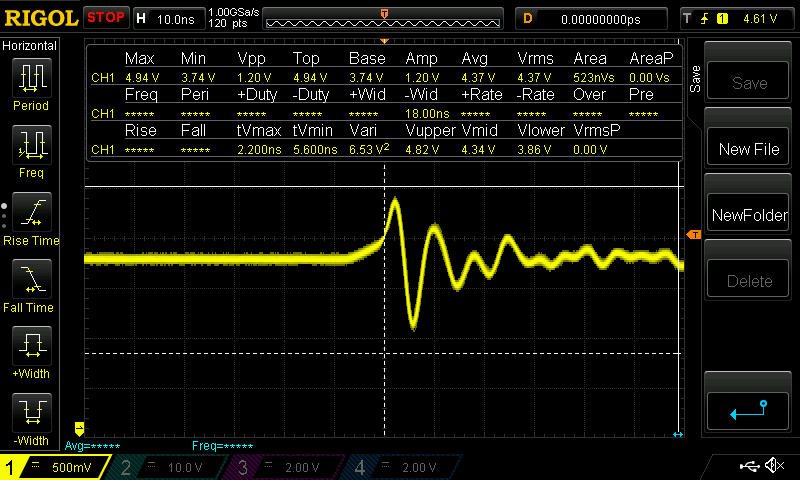

The voltage at the output is accurate but fall with more than 100mA. I've seen the signal (suposely square) at fet input has some damping (maybe bad layout) and with 1M resistor to ground there seems to hold more current at the output, but not too much.

I'm using 68uH inductor (CDRH127) and 33uF electrolitic capacitor at output. With 22uH (CD54) instead 68uH the current at the output is higher (arround 1A at 12Vin and 100mA with 30Vin) but when Vin goes up the supply goes down...

So I have two questions:

-Why TPS40200 is so extrict with components/layout when other DC/DC are not?

-What are the conditions fot TPS40200 to shutdown? (There is no Vin low here and I've increased the current with load so I think is not soft start related, there is not overcurrent...)

Thanks