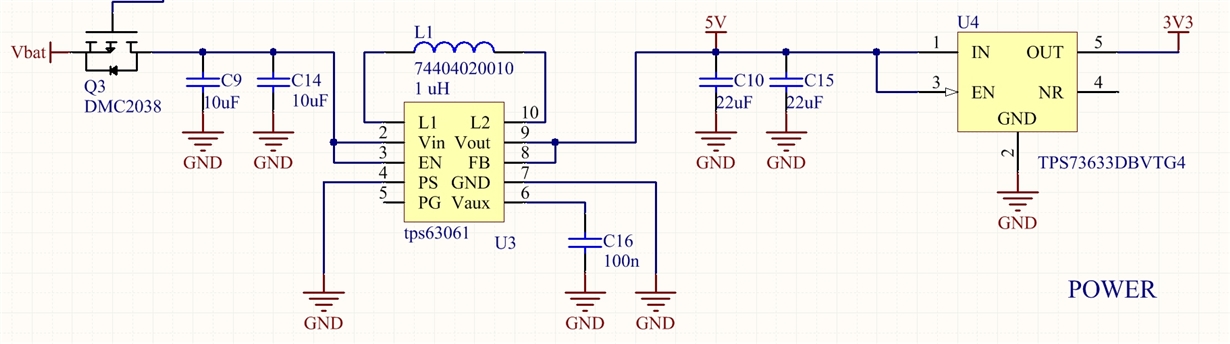

Hi! We are using this chip for battery powered application. Device has two options, either 4x AA or 8xAA battery on the input. We have realtively small batch of these devices made, all were functionally tested in house, then shipped to customers via airmail. When customers were using 4 batteries, everyhing was fine but when they used 8 batteries, device deid. Inspection showed that only thing that failed was TPS63061. Visual inspection didnt reveal anything, device doesnt look burnt, there is no shorts - no on input, no on output.

Unfortunately we werent able to recreate the failure in house, despite vigorus attempts of overloading the chip (over voltage on input, shorts on output...) so we are really in the dark here. Also, we dont have the access to an xray machine to inspect the internals of the chip...

Any help or suggestion will be much appreciated.