Hi Experts at TI,

We currently have a design using a TPS54560 that works like a charm. The only thing is that our requirements have changed and we need to see if we can’t squeeze a few hundred more mA out of the design, at least for short pulses < 100ms. We for, better or for worst, have mainly been using what Webench has been giving us. I’ve done maybe a few dozen calculations to make sure what Webench is outputting is accurate, and of course I’ve done physical testing.

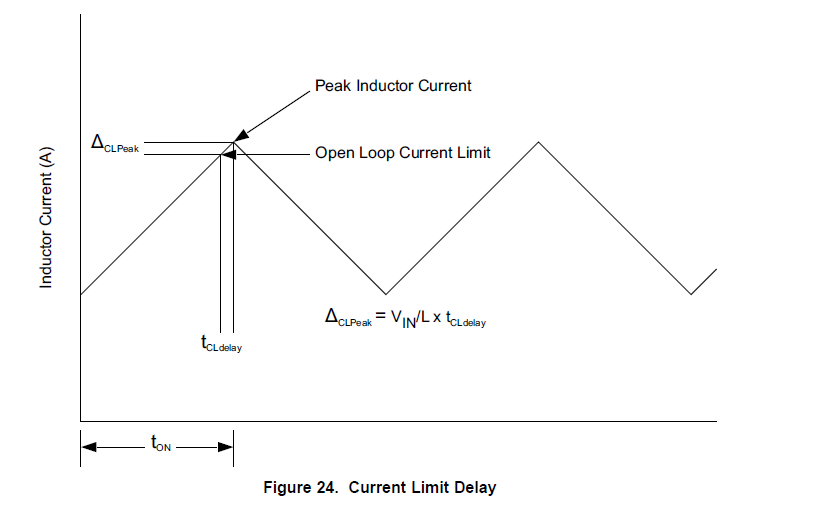

With that in mind I’m trying to get a better understanding of the current limits. I’m assuming that the 5A rating at the top of the data sheet is the max instantaneous current. So it’s at the very most it should be the maximum output current plus ½ the peak to peak current inductor current, and maybe a few hundred mA head room for transient responses. Does this sound right?

I’m also having a bit of trouble figuring out the limits at which the device starts to protect itself from over-current events. So is it correct to take the equation on Figure 25, and the Current limit threshold in section 6.5, and assume that is the peak current limit, aka the max current the inductor will see if it stays out of saturation?