Hello there,

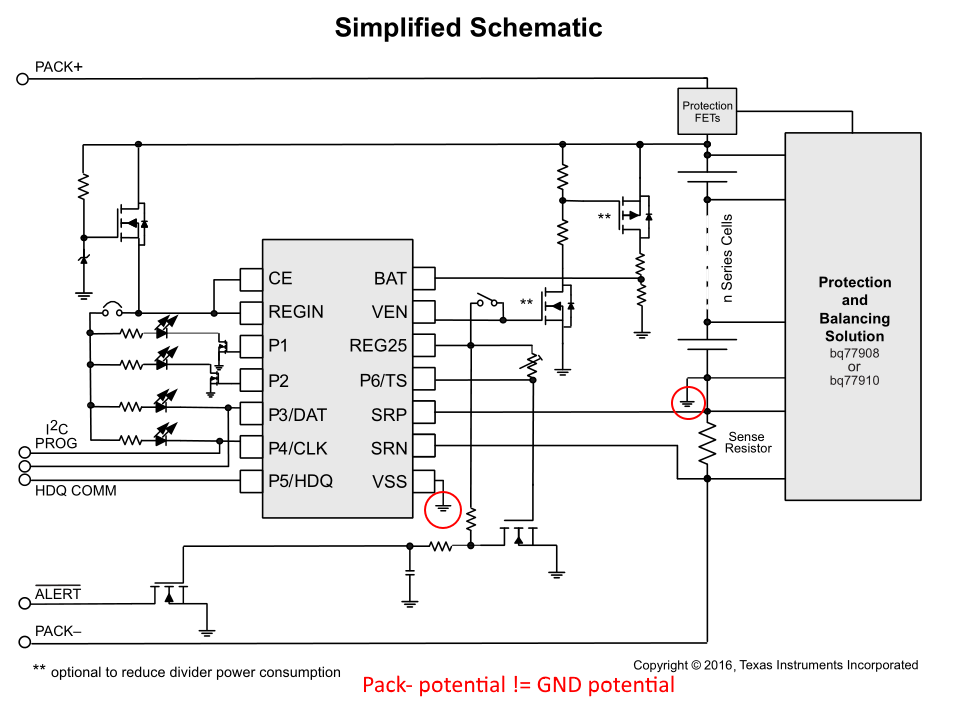

I am currently designing a board featuring the bq34z100-G1 device. Looking at the application note I am hacing some doubts either I understand everything correctly. Please take a look at the bellow figure from the datsheet:

As you can see above, the device GND will not be equal to the other circuitry GND connected through PACK+ and PACK-. In means of communication through I2C can cause trouble, since the external driver will pull to its own GND, and BQ will pull to the local one. The difference between grounds would be the voltage drop across R_sense.

Is this by design? I would really appreciate additional explanation, I need to move on with the design.

PS: I have noticed some inconsistency: The pinout table states that VEN is an OUTPUT, whereas from the description it seems as its an INPUT. Is this an error?