Hello.

I have a question about UCC24630.

Datasheet P5

VDRVST DRV pull-down in start-up

I have a question about pull-down.

1 It is supposed to work at start-up.

Does it function even when it is stopped?(VDD = voltage below UVLO)

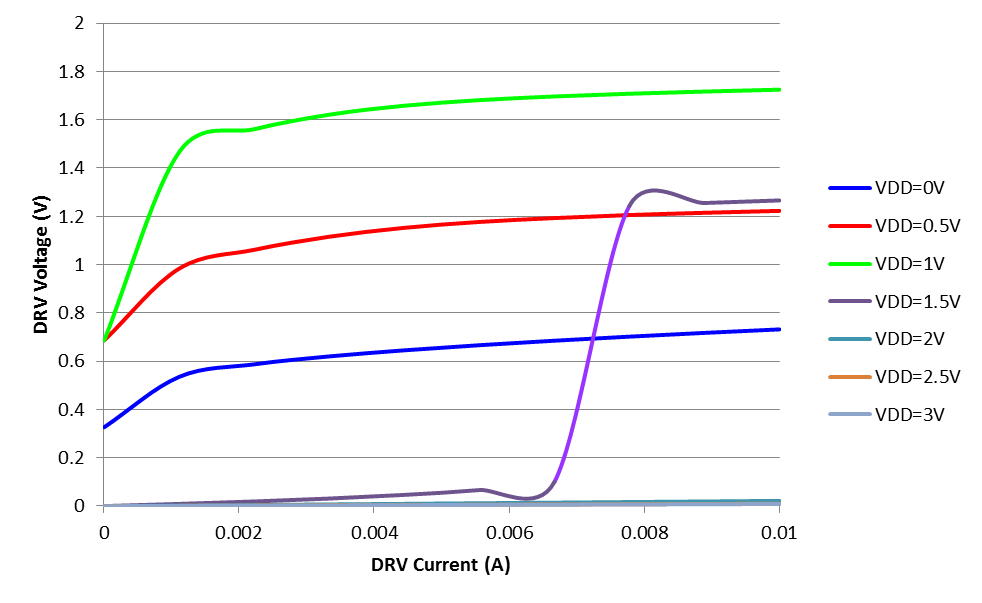

2 If the voltage of VDD is 2 V or less, is the voltage of DRV pin suppressed to 2 V or less?

3 If the DRV voltage is 2 V or less,

it is considered that a diode is built in the IC between the DRV terminal and the VDD terminal.

Is the diode actually built in?

If a diode is built in, please tell me the specifications (MIN, MAX) of Vf and If of this diode

thank you