Other Parts Discussed in Thread: UCC5310

Hi, do TI produce a gate driver IC with negative turn off capability without the need for a negative rail? I'd rather avoid gate drive transformers if possible so maybe a device using some kind of charge pump?

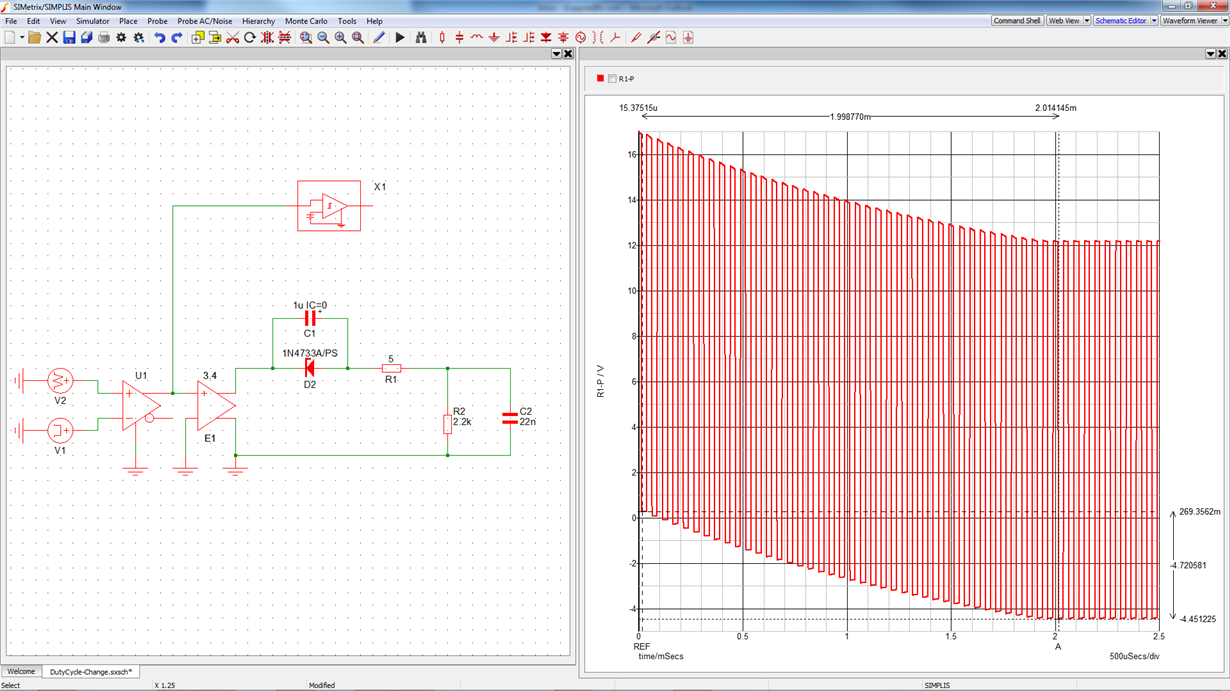

I ask as I have a problem with capacitive coupling turning the fet back on in my flyback supply, the spikes are caused by the drain to gate capacitance of the sihg73n60e mosfet. The gate drive voltage is 12v and the short spikes on the gate are only a few volts max but the turn on threshold for this fet is 2v minimum so it does cause it to turn back on slightly, I have a 2.2k pulldown resistor and 18v zener on the gate but that does nothing since the spikes are positive with respect to the source pin. Putting a turn off diode across the 12 ohm gate resistor fixes it but causes other problems due to dv/dt.

So I'm thinking +/- gate drive might be the way to go since I can't have the gate turn off too fast via a diode or other low impedance discharge path, going negative at turn off would allow the drain to gate capacitive coupling to still occur but since the gate will be negative it wouldn't allow the fet to turn back on,

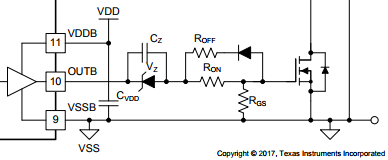

Do Ti produce such a device that could go between the UCC28C45 and MOSFET? It would need to somehow produce the negative voltage swing from a single 12v rail and be able to run at 20khz, non isolated is fine and the N channel fet is on the low side.

Thanks.