Hi Team,

Good day!

My customer is using our UC28025 for their project and have an inquiry on the soft start below:

We are currently tuning the soft start using your controller.

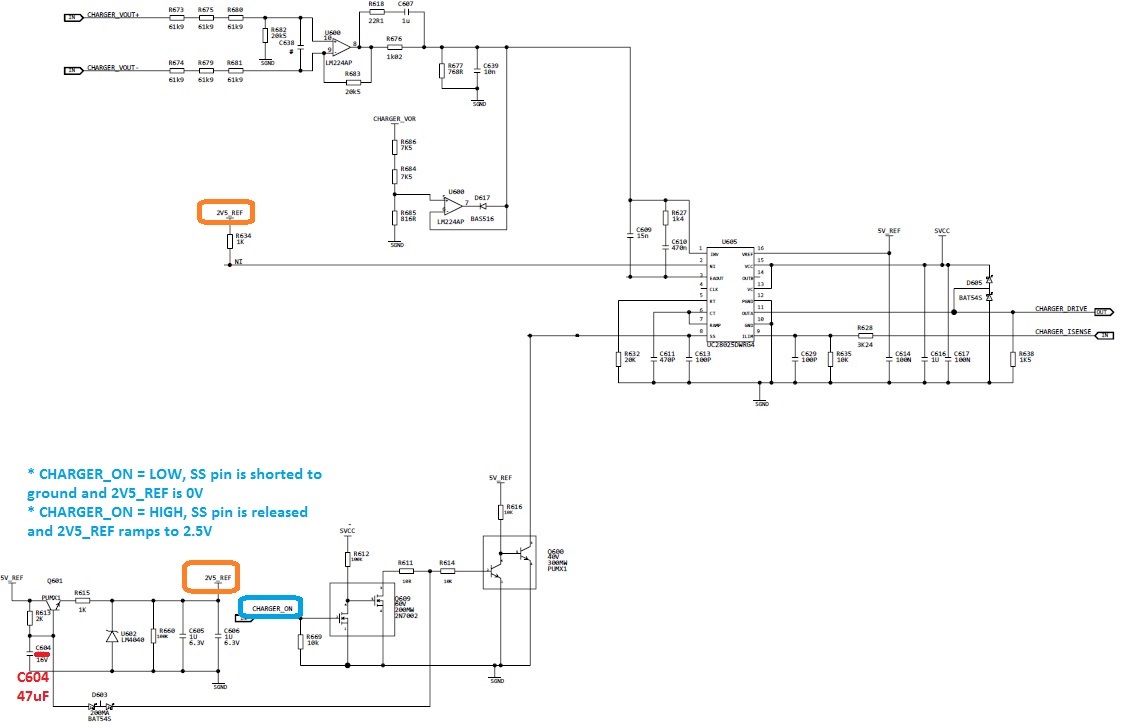

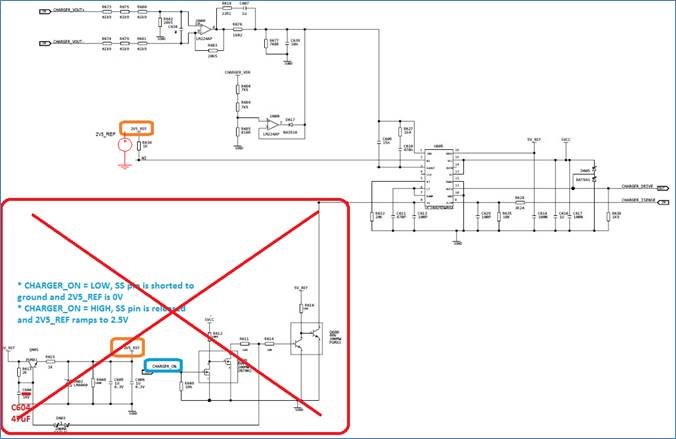

Attached is the schematic in our application.

We are using the CHARGER_ON signal to release SS pin and begin the soft start sequence. We do not seem to have trouble with this.

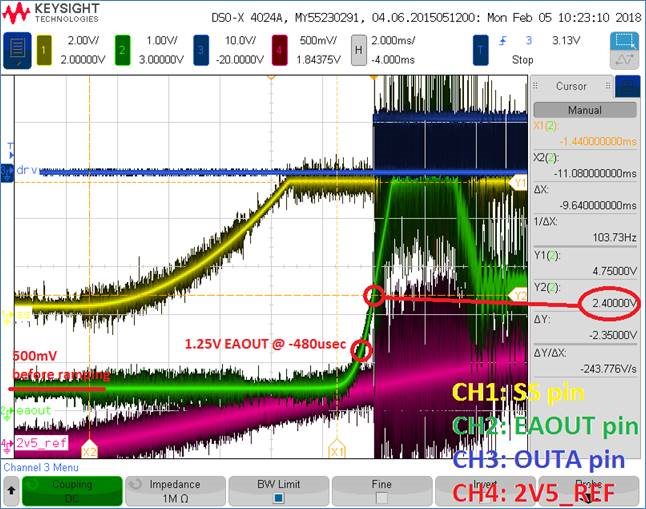

However, we do find it odd that the OUTA pulses only start 15msec after the SS pin has gone high.

Is this normal?

We are expecting that the OUTA pulses will start as soon as the SS pin is high. Is there an internal delay of some sort that prevents this from happening?

We are currently tuning the soft start by changing the value of C604—thereby delaying the 2.5V external reference’s rise time.

We want to delay the rise time of Vout as much as possible and to avoid having high overshoot.

Thanks!

Best Regards,

Alfred