Hello,

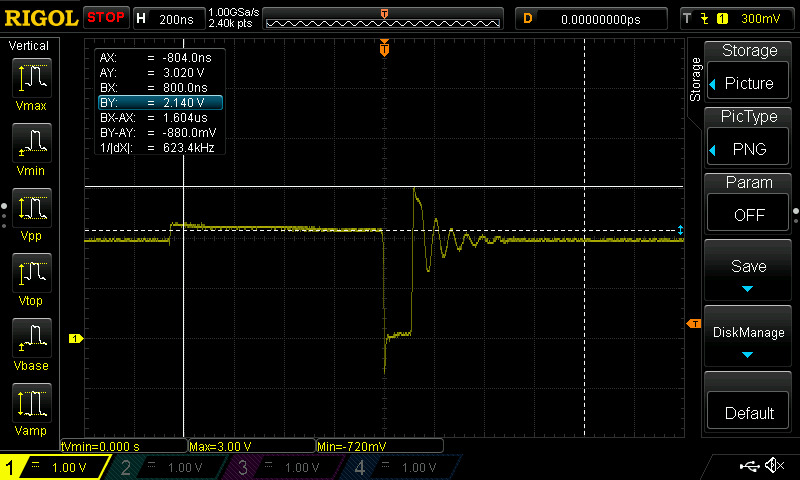

I'm measuring the voltage on SW node of the TPS62740 and I see these behaviour:

The absolute maximum ratings are:

-0.3V (in this case in more!!!) and Vin+0.3V (in this case more: Vin+880mV)

This behaviour is related to a not good compensation, usually. But i cannot act on the feedback loop (inside the chip).

Can you help me in this analysis, please?

Thank you and kind regards

Alessandro