Hello,

Regarding to VREG5(Regulator) on TPS565201, my customer is asking some question.

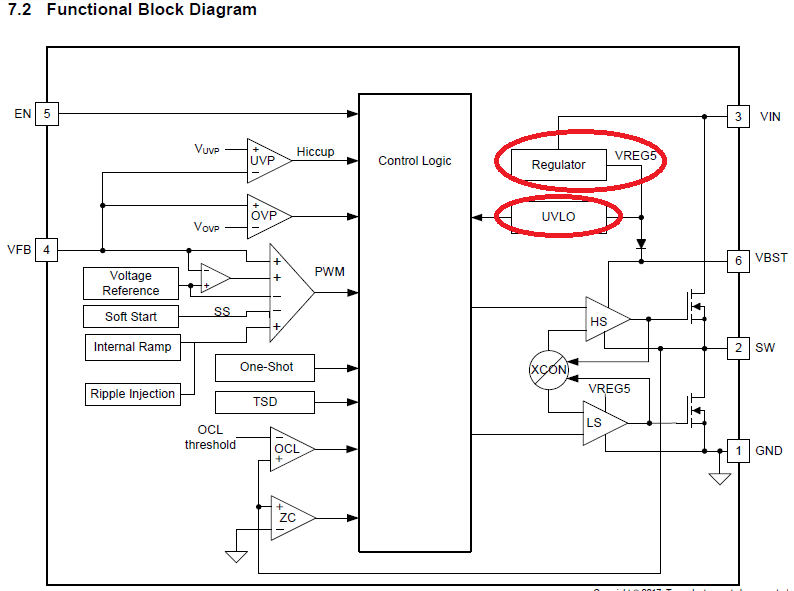

VREG5 is described in 7.2 Functional Block Diagram on datasheet(page9).

(Question)

(1)They understand that the conditions of VREG5 ON/OFF is by detecting High on EN pin.

Their understanding is correct?

(2) They understand that ULVO monitoring conditions of VREG5 is after VREG5=ON.

Their understanding is correct?

(3) UVLO threshold is described in 6.5 Electrical Characteristics on datasheet(page5).

(Wake up: 4.0(typ) ,Shutdown:3.6V(typ))

Is it meaning the specification of UVLO in 7.2 Functional Block Diagram?

Regards,

Tao2199