Other Parts Discussed in Thread: TINA-TI, , UCC29002, PMP8740

Tool/software: TINA-TI or Spice Models

Support Path: /Product/Find help on educational technology and calculators/

Hi,

I must developp a power supply system with the following electrical characteristics :

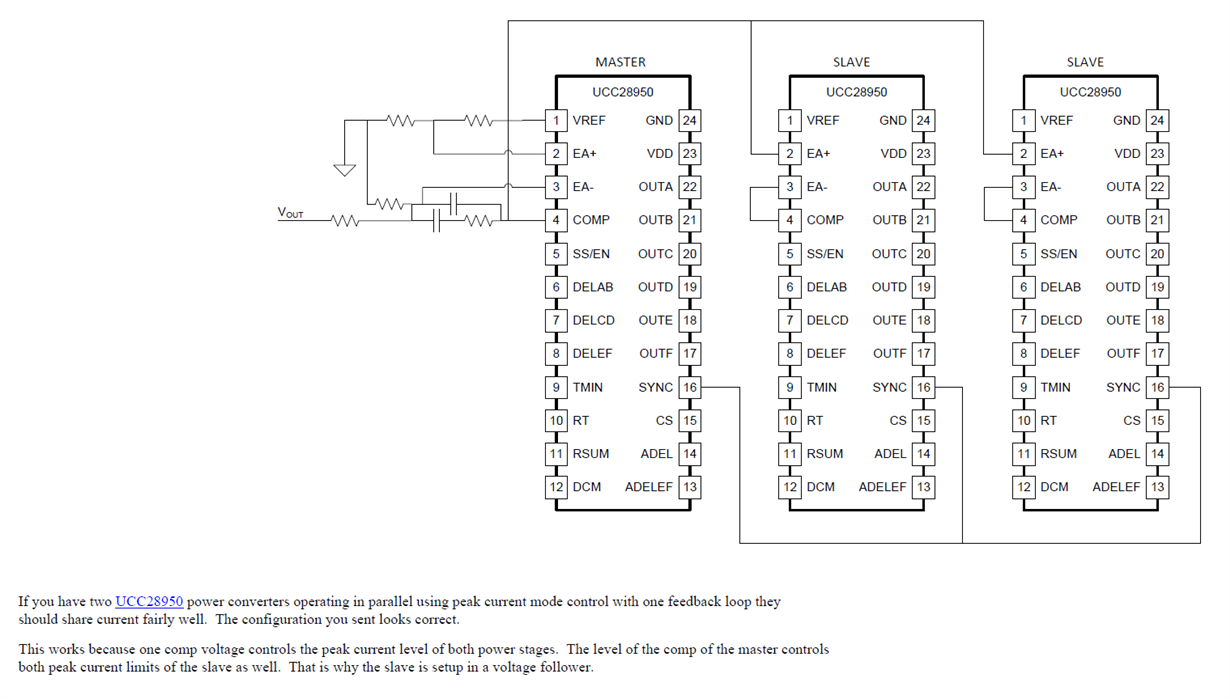

- 3 parallele power supply modules in order to provide more electrical power

- each module use "ZVS Phase-Shifted Full-Bridge converter" topology based on UCC28950 controller with synchronuous rectifier.

- on each module use an UCC29002 to share current between the 3 power supply module.

This architecture looks like the PMP8740 developped by TI (refer to slup349 document).

I have several questions about PMP8740 power supply module :

1. design justification document :

Have you got a design justification document (besides to slup348 and slup349 document) ?

2. voltage feedback :

.

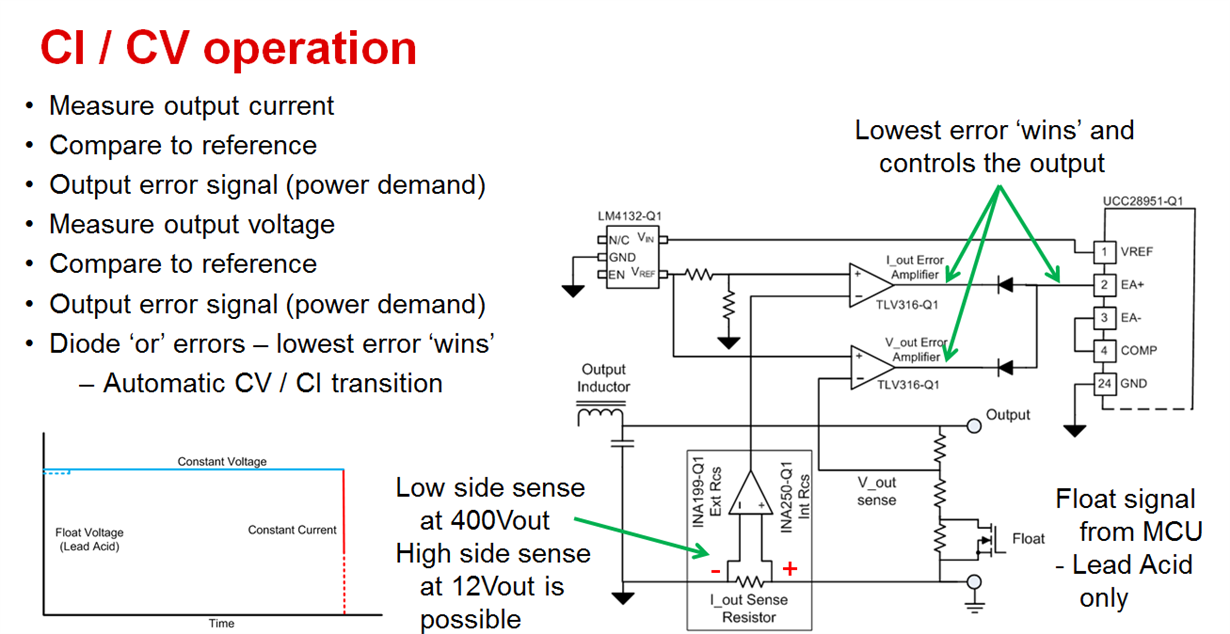

I don't want realize a current loop, voltage loop is enough for my application.

Into voltage loop, why IOUT (power supply output current) is used into this voltage feedback ?

Bests Regars

Benoit PINARD