Hello,

I wanted to understand UCC28704’s short circuit response. Is my understand of events below correct?

- Short circuit

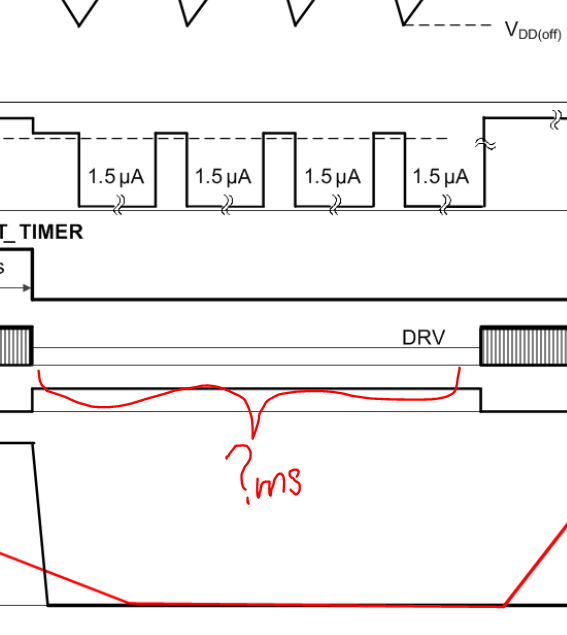

- UCC28704 operates in cycle by cycle current limit for 120ms (tblank of CCUV)

- UCC28704 enters 3 cycles of VDD_UVLO

- Restarts at the power up of the 4th cycle and restarts step 2 if fault persists.

If correct, can you help me understand how long those 3 VDD_UVLO cycles take?

Thanks,

Rohit Joshi