Hello,

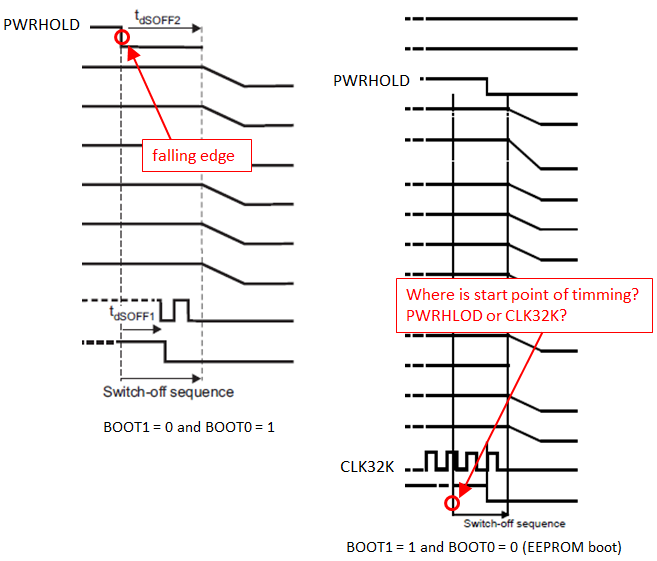

Regarding to switch-off sequence time at power down on TPS65910Ax(EEPROM Configuration mode) ,

my customer is asking a question.

(Question)

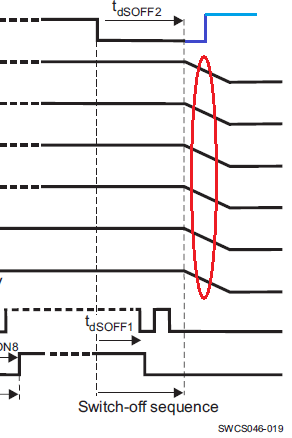

(1)The contents of switch-off sequence time (tds OFF2) is deferent between datasheet Figure 5-2(page 39) and User's Guide Figure 3 (page6).

They think that datasheet Figure 5-2 will be correct. Their understanding is correct?

(2)After tds OFF2, when power-up is executed again by PWRHOLD(L->H) at remaining some output voltage, is there any impact to TPS65910 or AM335x?

(When power-up is executed again remaining some output voltage, is there any problem?)

The each output capacitor value are same as schematics of AM335X_ICE Board.

Regards,

Tao2199