Other Parts Discussed in Thread: TPS3890-Q1

Hi There,

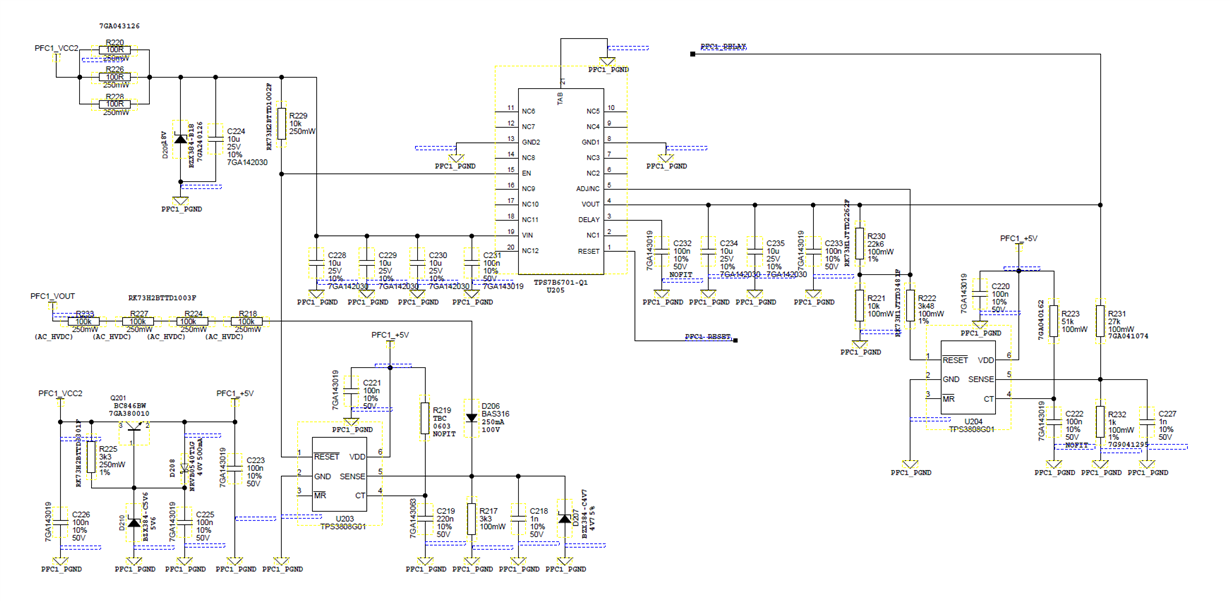

I appreciate there is more than one TI part here, but I am keen to understand if the TPS3808-Q1 (please ignore the EVM part number in the schematic) would work here as a delayed switch to set the LDO to 4V. I will also include the thought behind the rest of the circuit to help give some system background.

The LDO (TPS7B6701) in question is powered from 12.25V (PFC1_VCC2).

The IC, U204 will switch to 4V after 200ms. The LDO is not active until 1 second when the PFC1_VOUT is higher than the threshold.

The LDO RESET signal will be pulled up externally and connected to a micro for additional control.

Many thanks in advance for your help with this.

Ross