Other Parts Discussed in Thread: UCC28951

I tested my circuit with power section. My input voltage is 120V and o/p is 24V in CV mode. I am using external error amplifier. R7 is open and Output voltage feedback is only used. Vdac is set point and Vo_adc is o/p voltage f/b. Ideally when these two values match, EA+ should go low and UCC should control it as CV mode.

Ea+= Vdac-Vo_adc ...(unity gain).

When I give Vdac =1.5 V and when Vo_adc = 0.7V, the system becomes unstable and magnetics start making noise and the unit enters in Desat protection. This happens aroung 0.8V @ comp pin.

1. Should the opamp U45 be unity gain? (All its resistors are 10k making it unity gain differential amplifier).

2. Will the compensation loop values effect the basics controlling of the system? I tried changing it and calculating it based on the datasheet but there is no effect.

3. What will be Rsum effect?

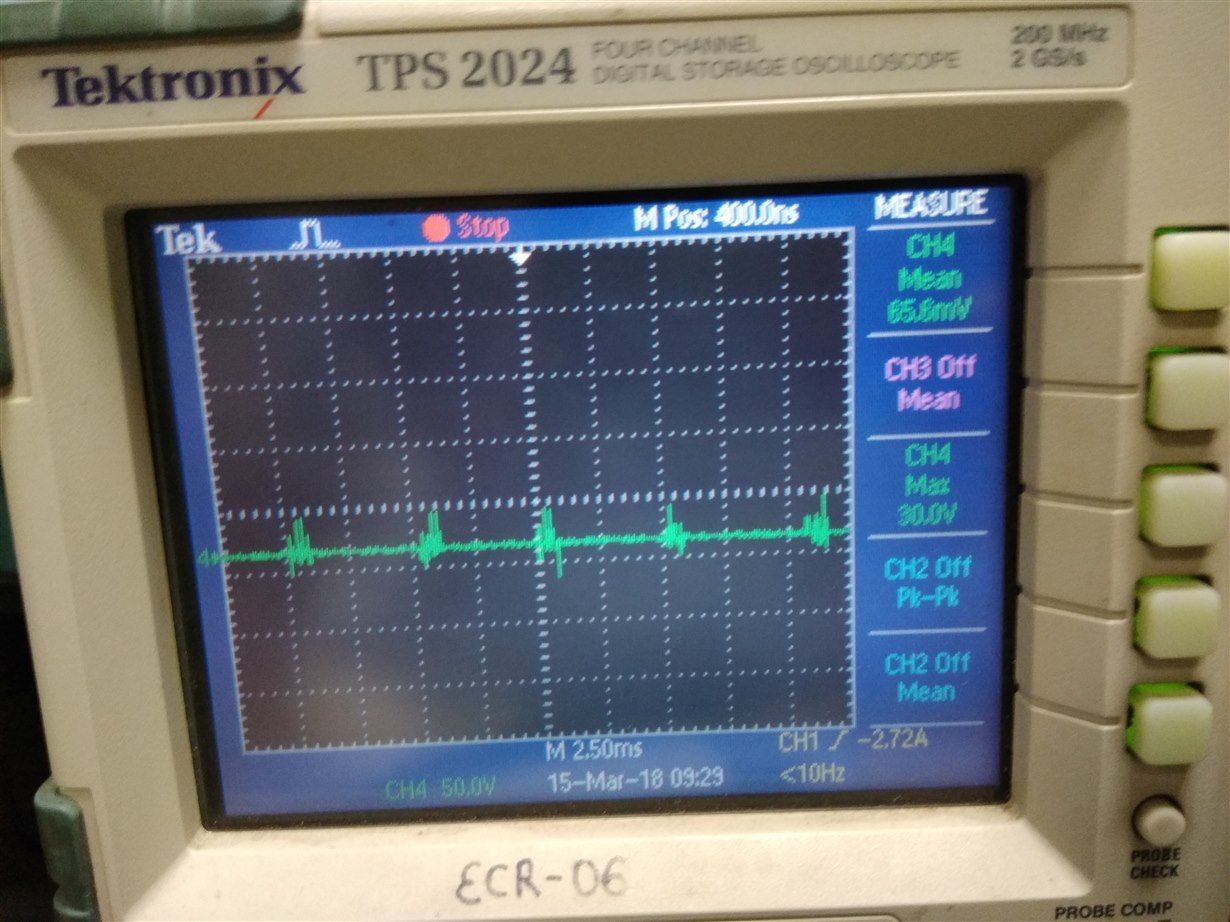

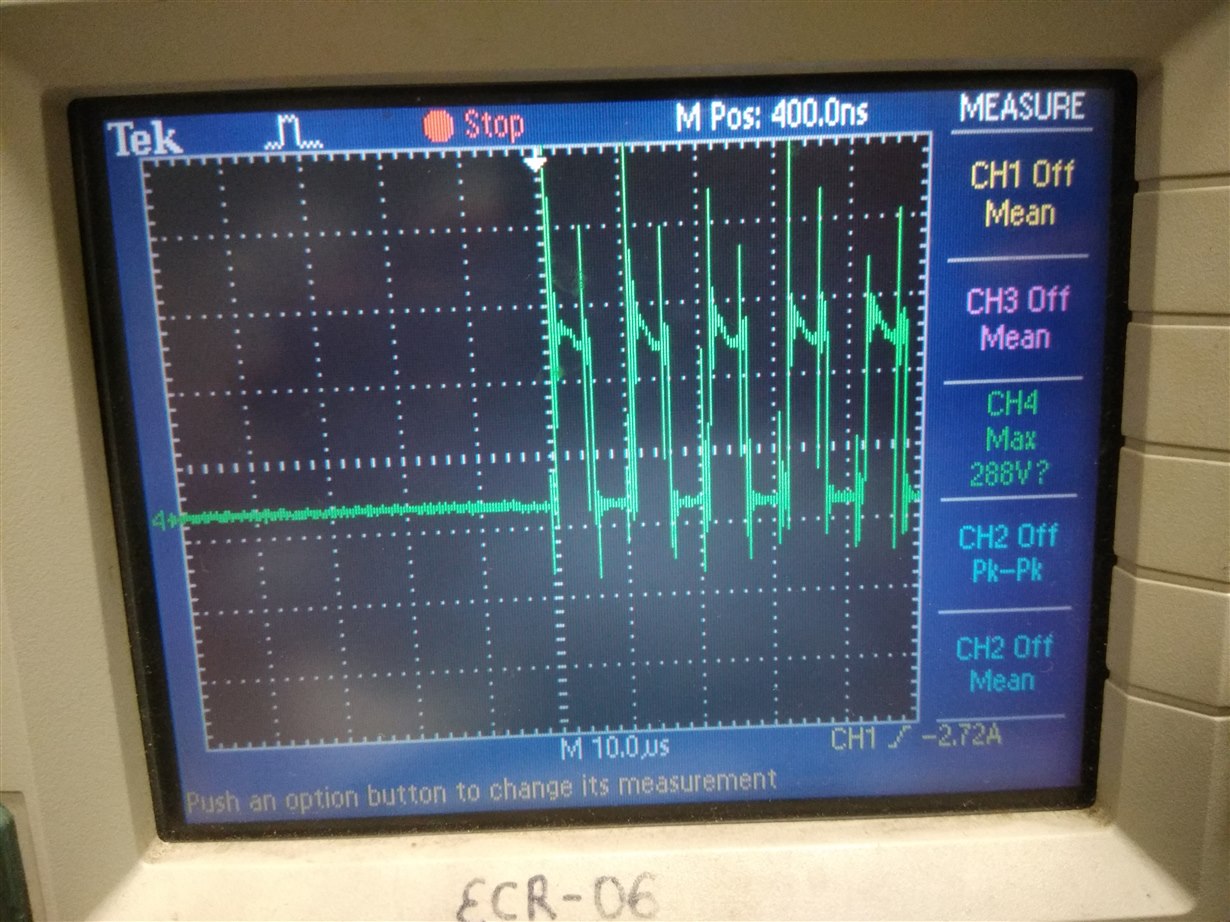

4. When I remove the voltage feedback the system gives 30V uncontrolled o/p at 95V i/p. Transformer is 4:1. But when I connect the f/b, the system starts misbehaving as mentioned above i.e. at 35V i/p and 9-10V o/p the magnetics start making noise and then there is desat. The Gate, Drain waveforms are very noisy and unclear.

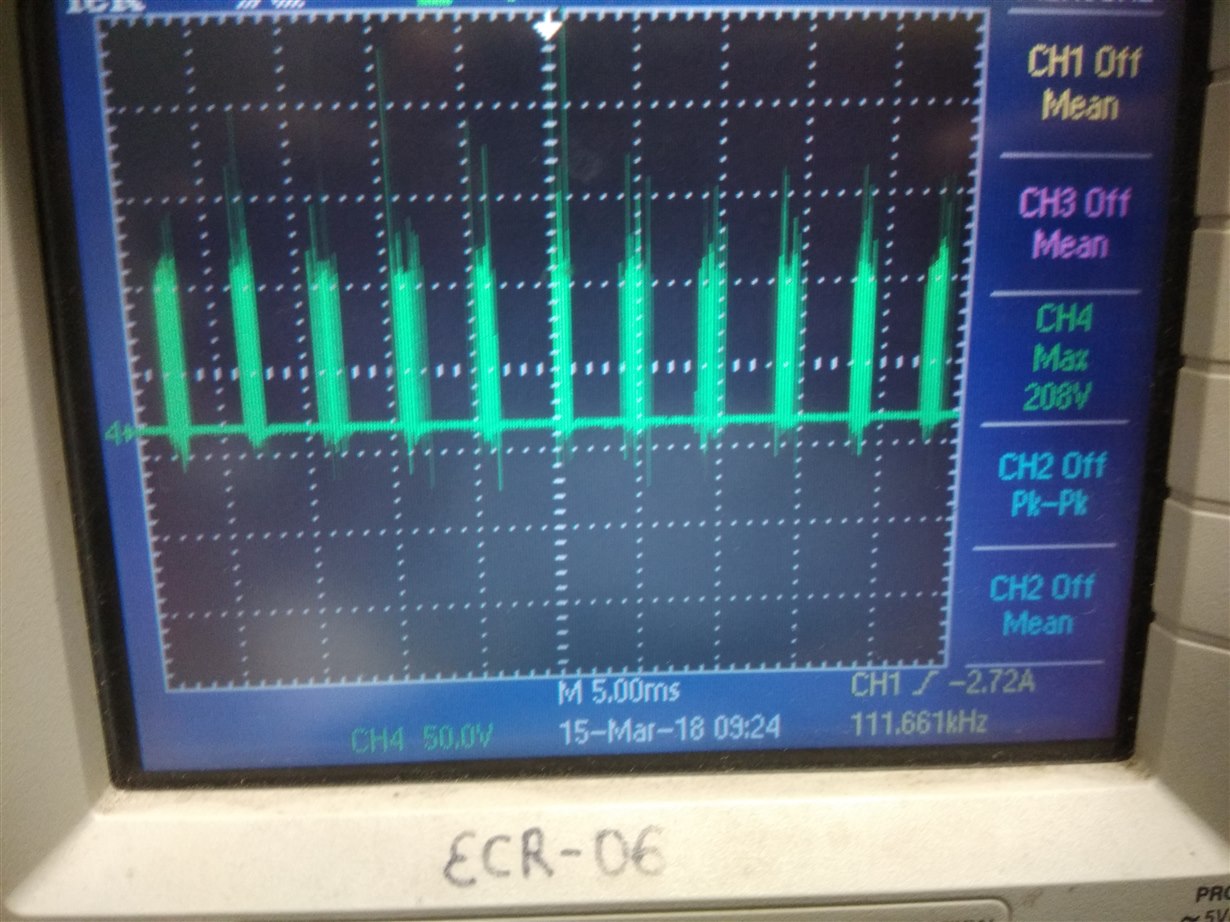

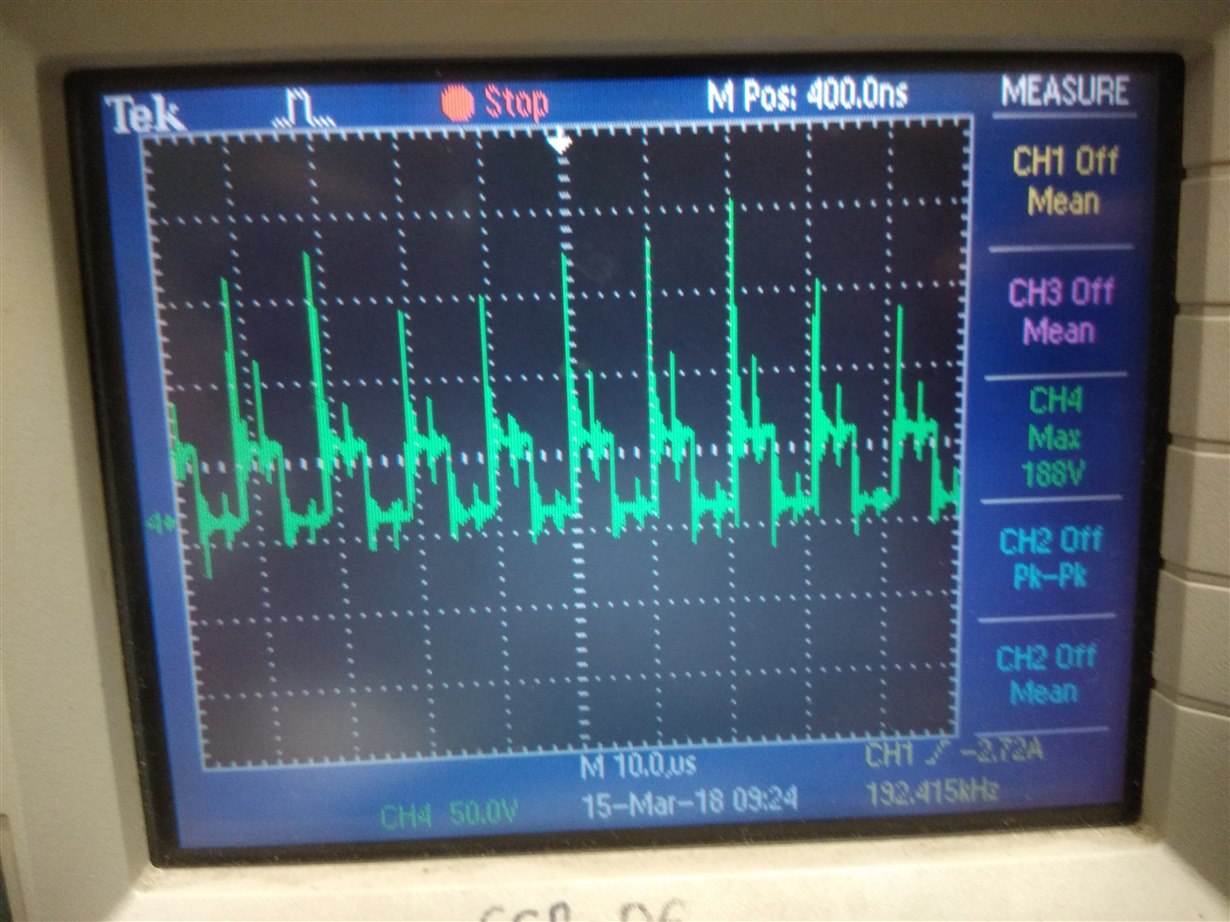

Also, after making R123, R53 = 0ohms, and when set value for output voltage is kept at 16V then the controller keeps duty cycle at max till 64V (4:1 transformer) and after that if i increase the input voltage the duty cycle should vary but instead it directly goes into burst mode with changing the phase shift between switching MOSFETs. The magnetics starts getting noisy thereafter.

Can you suggest why the duty cycle is directly going from Dmax to Tmin burst mode?

Please suggest what should be the circuit values for making this work. Please let me know the effect of Rsum and Comp pin voltage.

Thanks,

Jignesh C. Patel