hello

In SLUA560C in equation no 122 from where that 2.25 is coming? is it related to zvs from 50% to 100%? When refered SLUA107A it is given that

Why it is that tank frequency FOUR times higher?

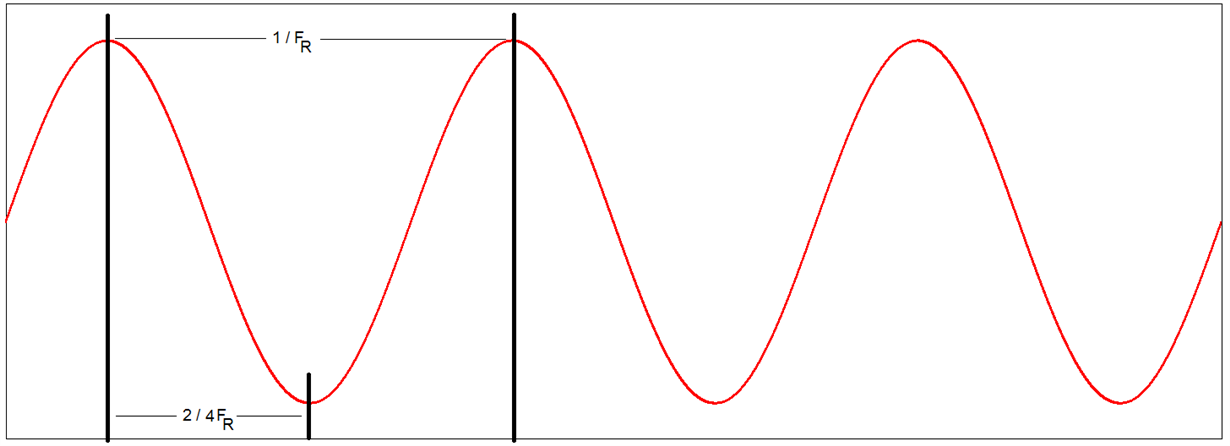

and if you put last equation in terms of frequency and rearrange. it comes out that Tmax= 1/(4*fr) where fr is resonant tank frequency in Hz.

so were is that factor 2.25 is coming in equation no 122. and factor 2 in equation no 75?

please explain.

thanks

samrat