Hello,

Regarding to power-off at EEPROM mode on TPS65910AA1, my customer is asking a question.

(Question)

・In this mode, does it need DEV_OFF or DEV_OFF_RST control bit for power-off?

According to datasheet page 47, these control bit are set to 1 for power-on disable.

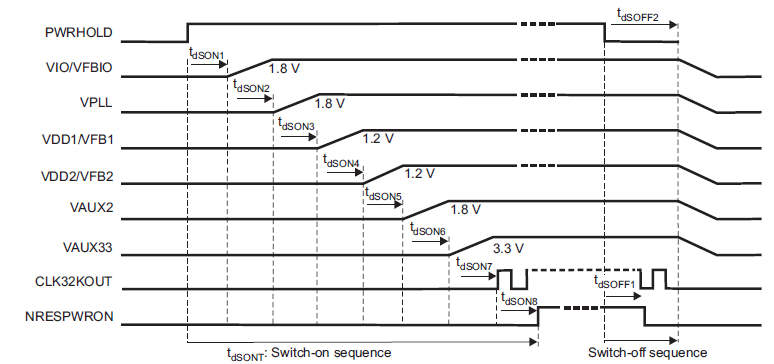

But it seems that power-off sequence is started by falling edge of PWRHOLD on figure 5-2 (D/S page 39)

and figure 3 (User's Guide page6).

Is only PWRHOLD control needed for power-off at EEPROM mode?

Regards,

Tao2199