Hi,

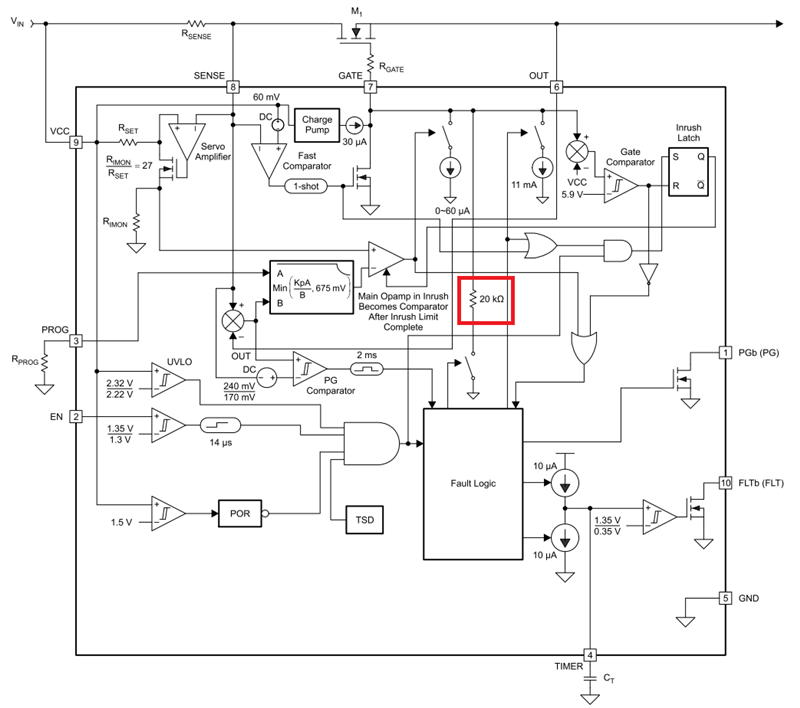

There is mentioned on page 14 of TPS24710 data sheet that the GATE pin is discharged by a internal 20kΩ resistor to GND if the chip die temperature exceeds the OTSD rising threshold.

So, is the GATE pin discharged by a internal 20kΩ resistor as well when pulling the EN pin to low ?

If yes, is it possible to apply a bias voltage(1V ~ 1.5V) to the GATE pin with external divider resistors(the low impedance) when pulling the EN pin to low ?

Best regards,

Kato