Other Parts Discussed in Thread: TIDA-00778

Hello,

Condition reported few weeks ago was thought to be leakage of HB since no FET's were yet installed. Sadly reported condition remains after they were installed both HO/LO gate drive.

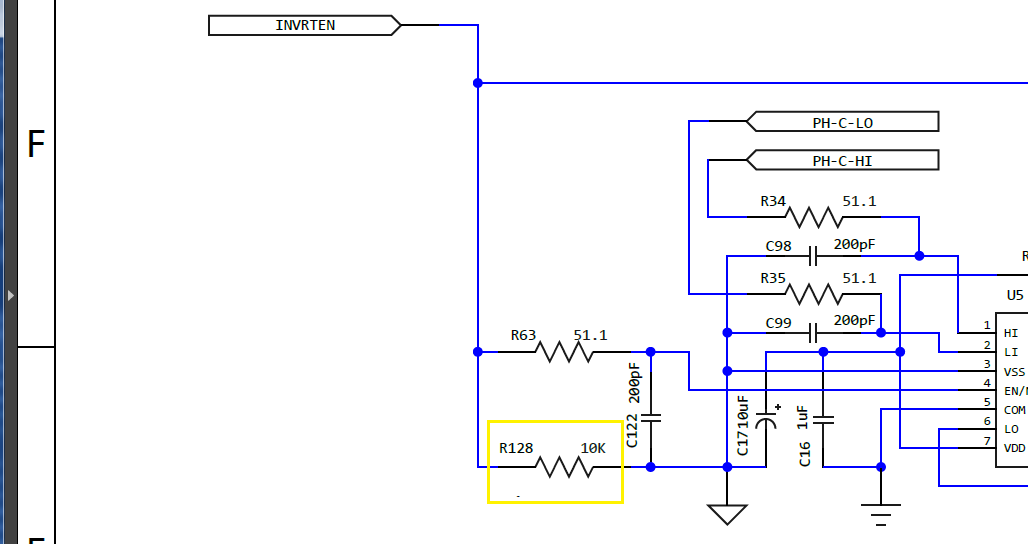

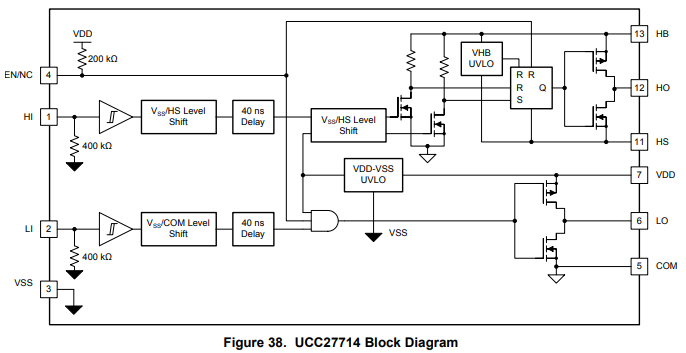

POR of MCU PWM pins 1/2 (pull down 20k) and GPIO drive EN pin 4 to three UC devices have EN line pulled down 10k is 0V when HO goes high.

Power supply +15 VDD has 2.97ms delay up to 80% of 3v3 MCU power capture posted below. These UC have been setting HO high on POR and do not follow truth tables in datasheet. Made sure to solder iron temp 258*C for less than 10 seconds per pin most were done in less than 4 seconds, solder to pads look very clean not cold. Have 20k/16v zener in parallel across HS/HO pins 11/12 and measure +13v on either pin.

What is causing the HO to stay on all the time, seems LO is keeping 0v during POR. Any PWM drive to pins 1/2 cause 1/2 bridge shoot through with MCU Panic shut down.

Applied power to system: HO to VDD rise: