Dear experts,

We met power-up issue with TPS65217C. We can measure correct SYS voltage after sourcing power to VBAT(3.6V) or AC(5V).

We connect SYS to VIN_LDO as recommanded. From the datasheet, LDO1 voltage should come out directly with SYS voltage, but we cannot measure that. (There is no loading on VLDO1)

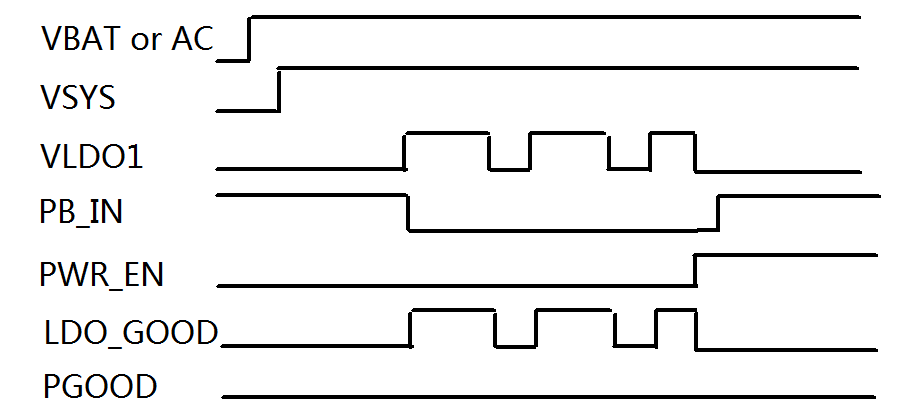

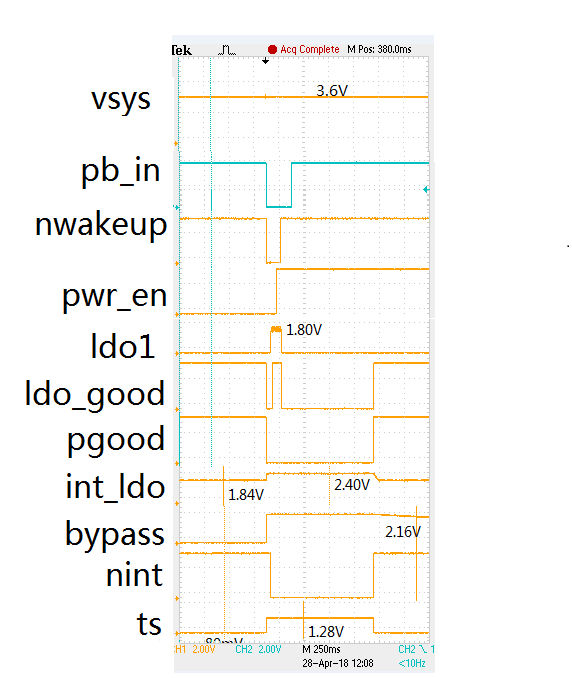

When we hold PB_IN low, we saw 5s + 3s cycle which looks similar to "Wait PWR_EN timeout" and "PB_IN reset":

-in 5s period -> LDO1 output is 1.8V, LDO_GOOD is high, PGOOD is low.

-in 3s period -> LDO1 output is 0V, LDO_GOOD is low, PGOOD is low.

-once we pull PWR_EN high, the LDO1 output drop to 0V.

-if we pull PB_IN high, after this 5s period, LDO1 output drop to 0V and never go back to 1.8V.

Could you help us on this or let us know if you need extra INFO or experiment. Thanks very much.