Hi Ti,

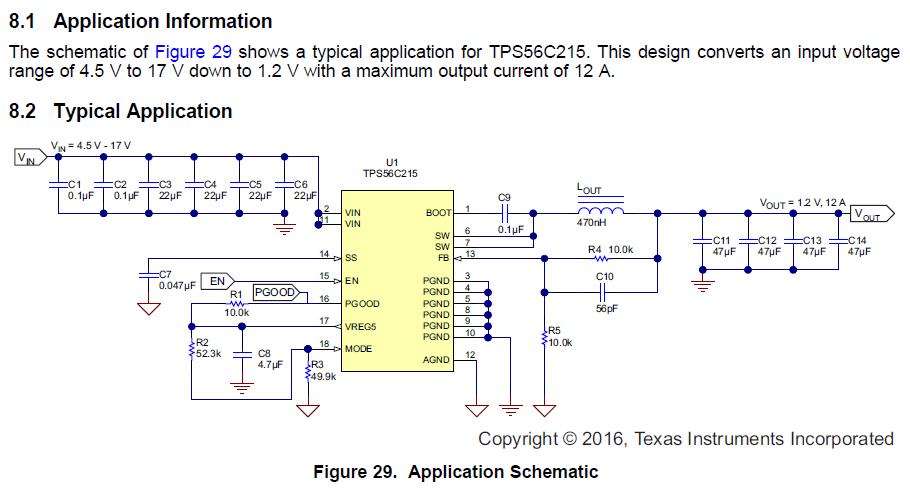

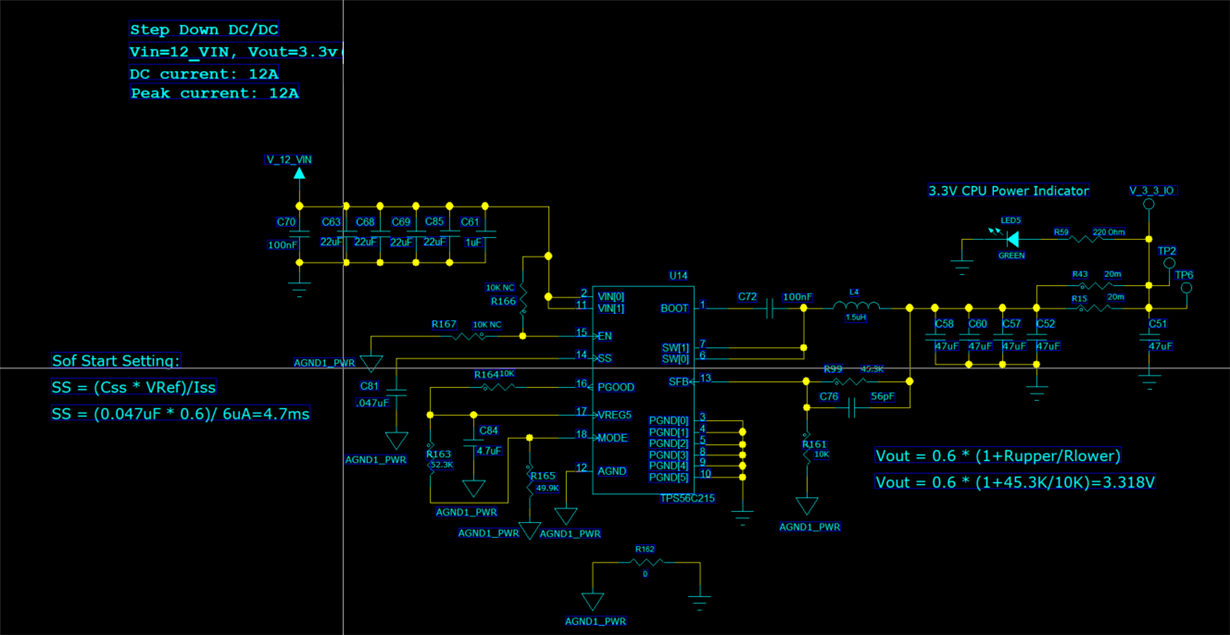

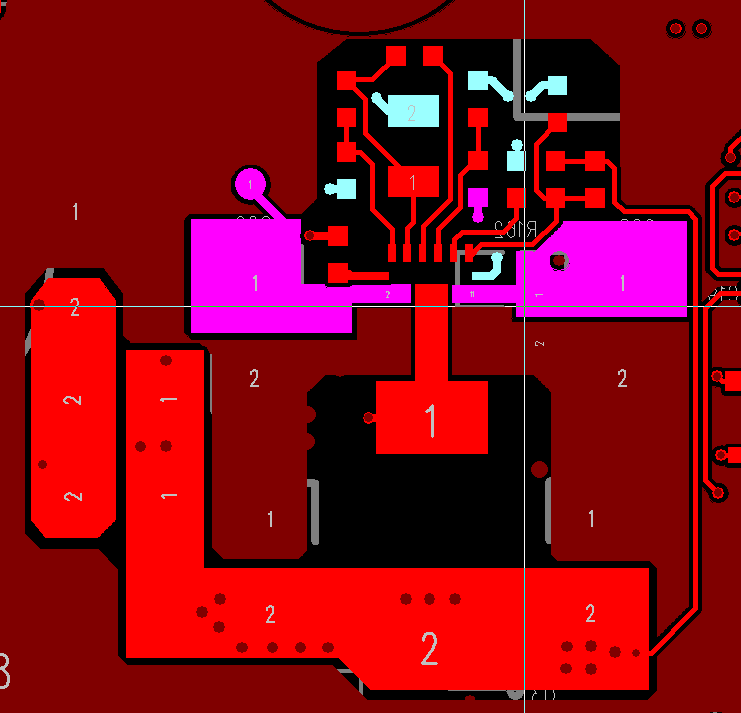

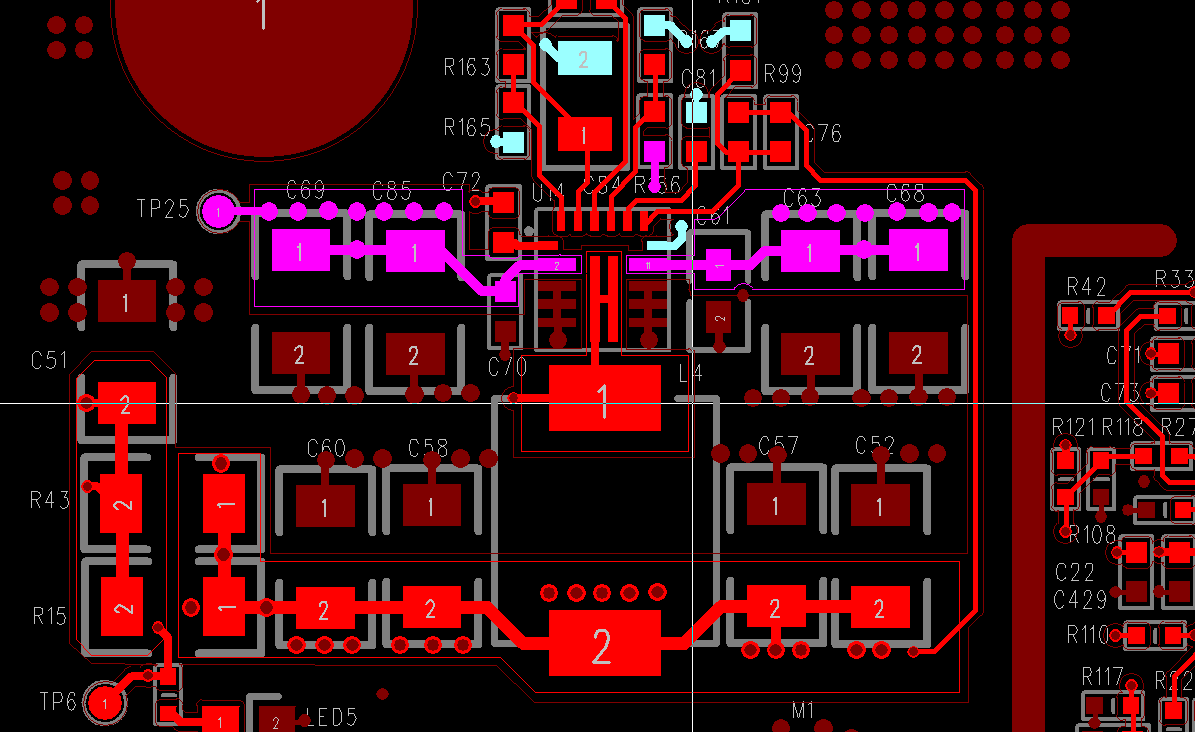

I have questions and concerns using the TPS56C15 on the CPU main board. Looking at the reference design, there are 2 grounds (analog and digital) and combine them at one point. I have it on my CPU board, and with the full system load, the moment we try to change some settings, it resets the board. See below reference.

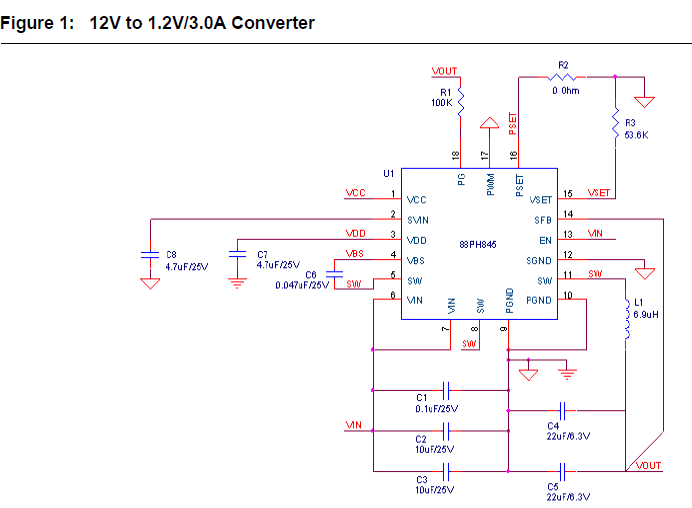

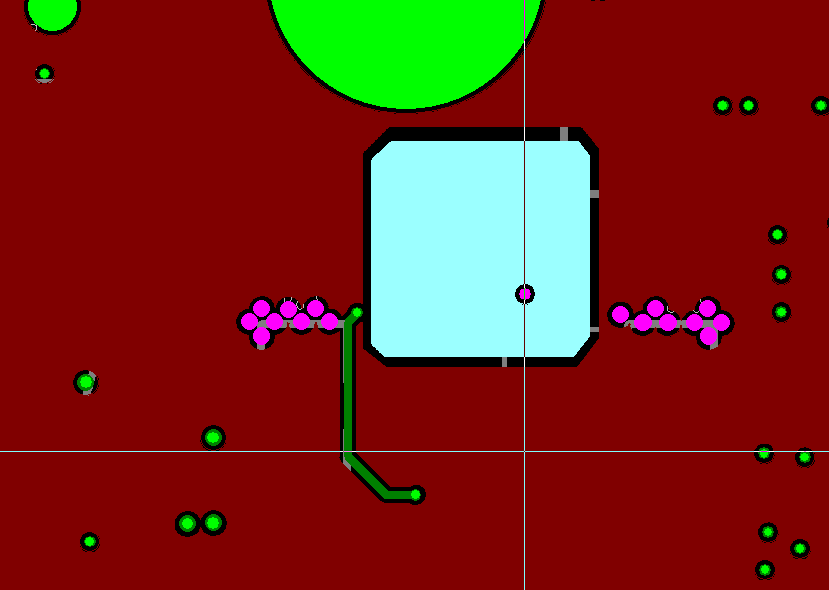

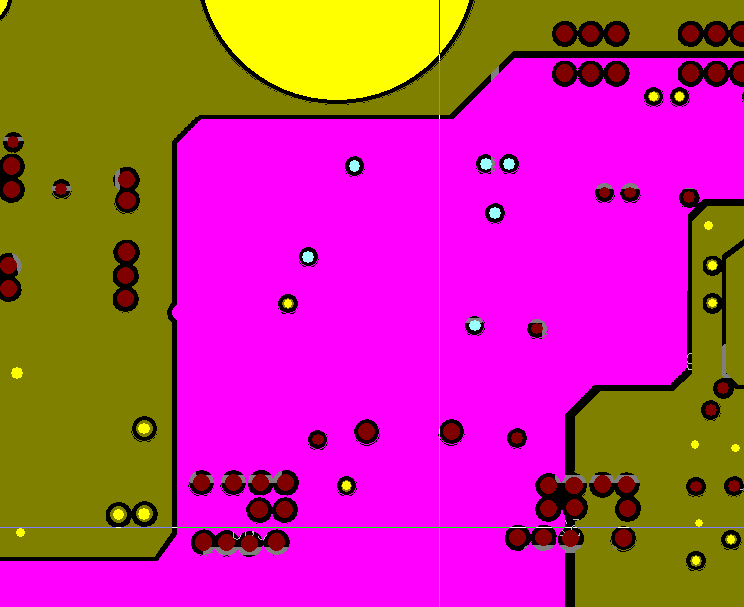

I used marvel supply with no separation of ground, and i never had this issue. See below Marvell, but ignored the 2 grounds, and use it as 1 common ground

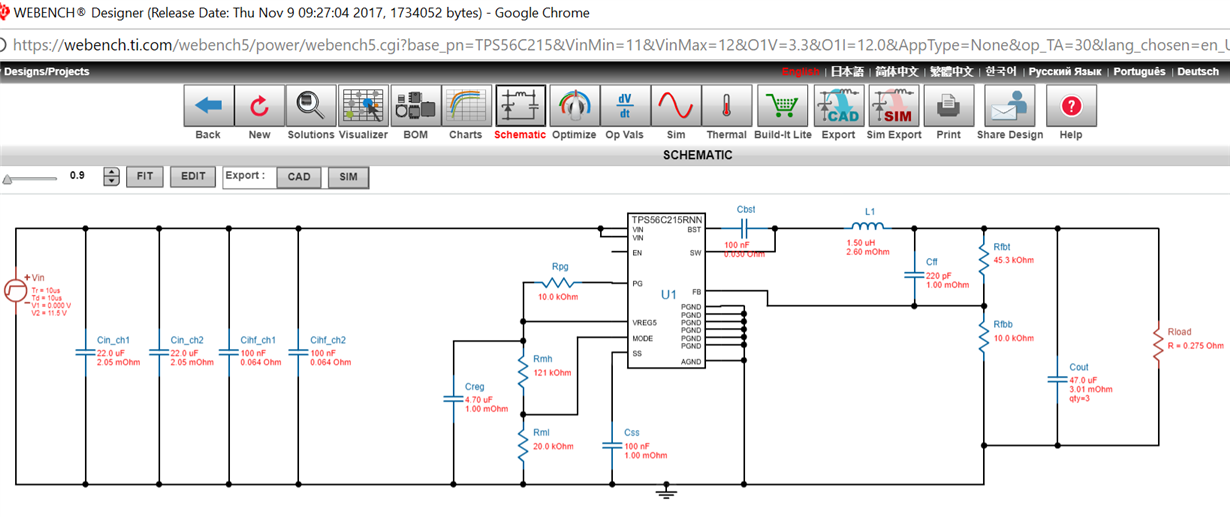

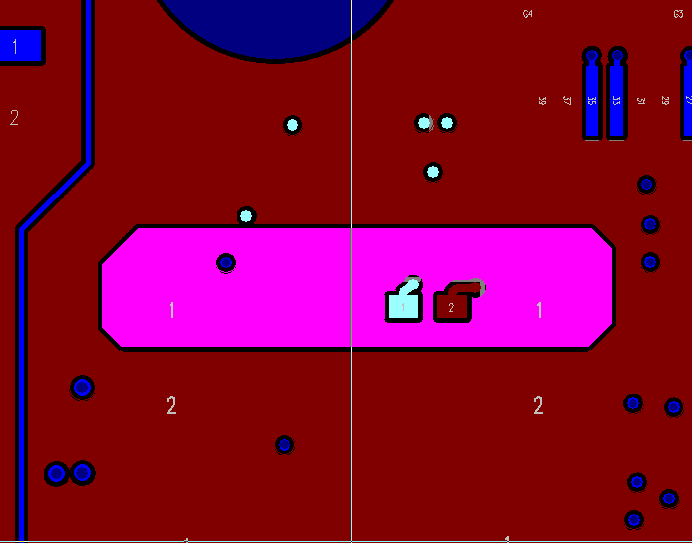

Why are we having this issue if i isolate with 2 grounds,and if i use one common ground, I believe that should able to solve it. From the TI website the workbench showed it as one common ground. see below schematic.

Please help to advise further.