Other Parts Discussed in Thread: ALLIGATOR

Hello all,

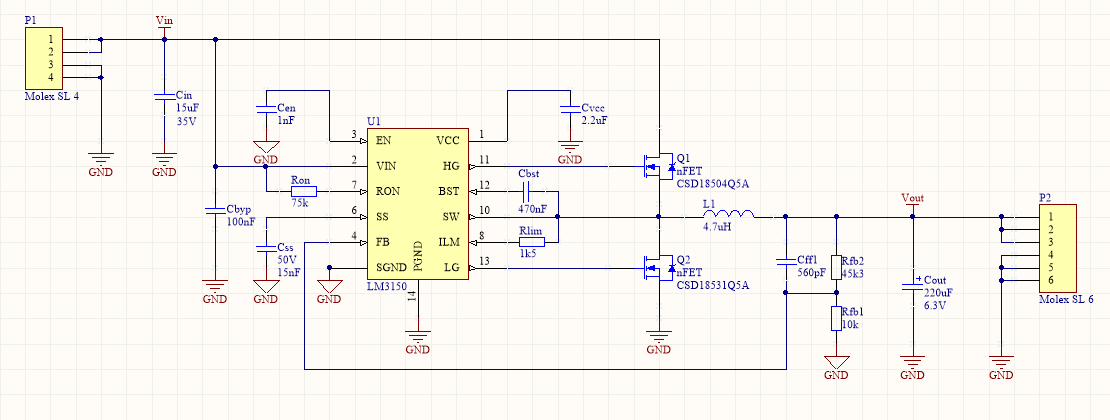

I'm currently struggling getting the LM3150 running. Three voltages are planned: Vout 3.3V, 5V and 12V, Iout: 6A. Vin 12-24V (Vin > 15V when Vout = 12V). The schematic is based on Webench, with minor deviations (3.3V version shown here):

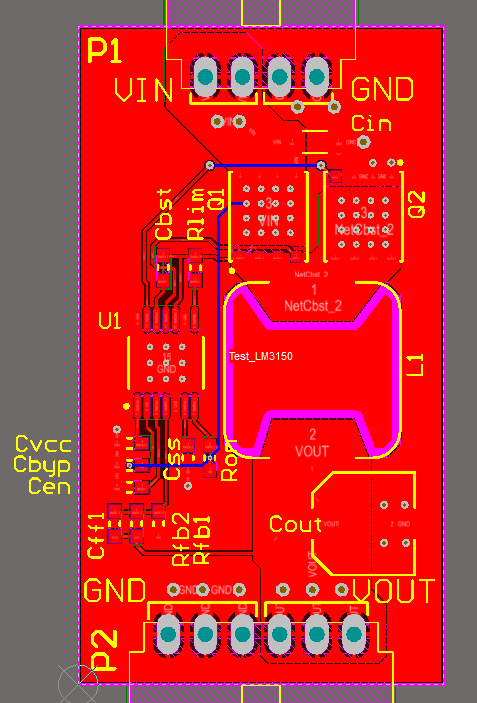

(GND polygon on bottom layer hidden. Pink shape under inductor is a keepout area on the top layer)

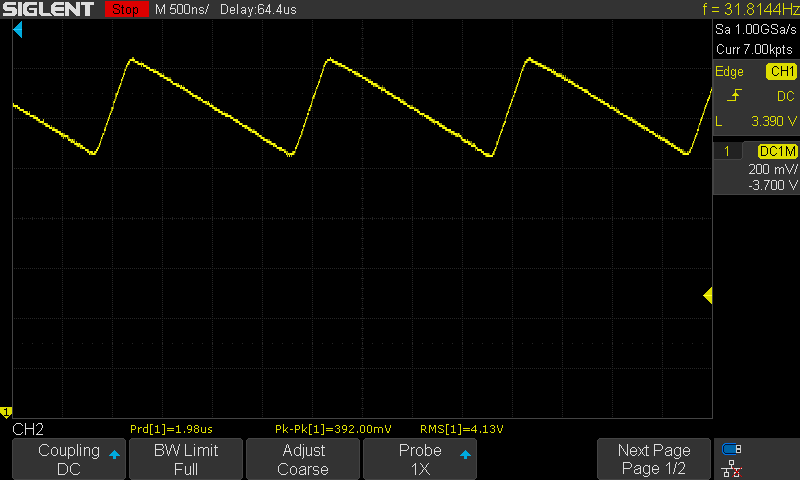

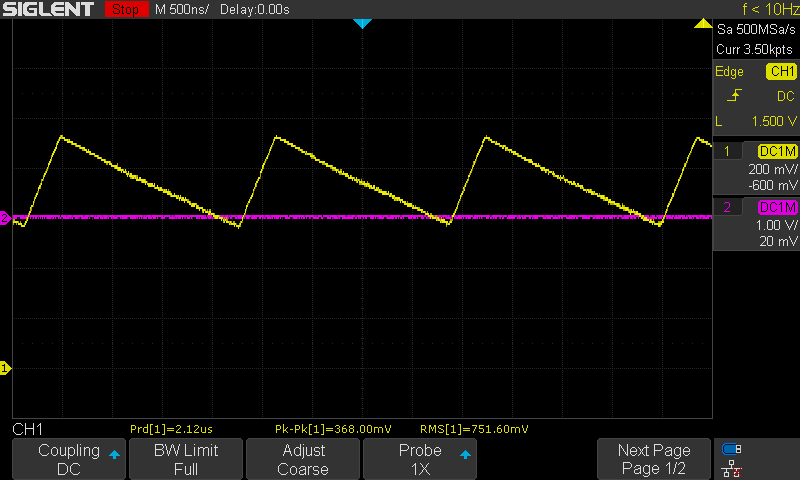

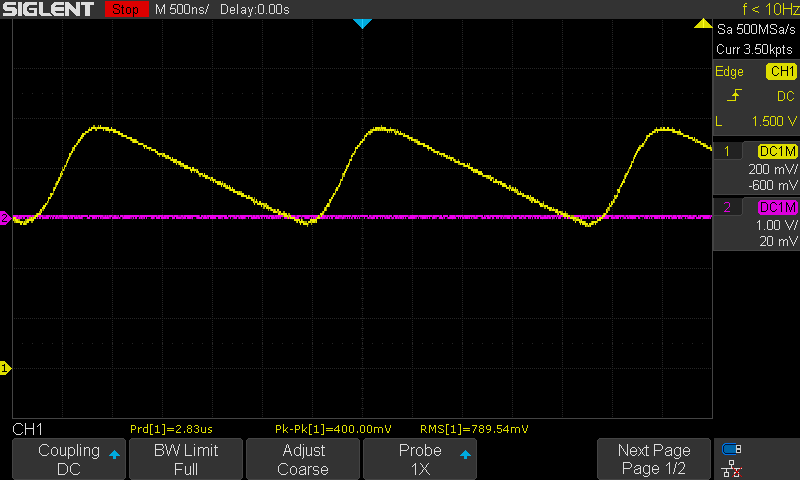

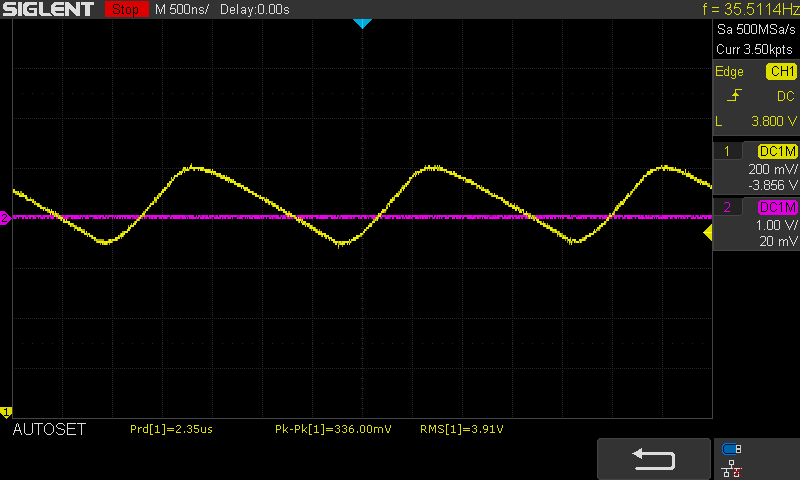

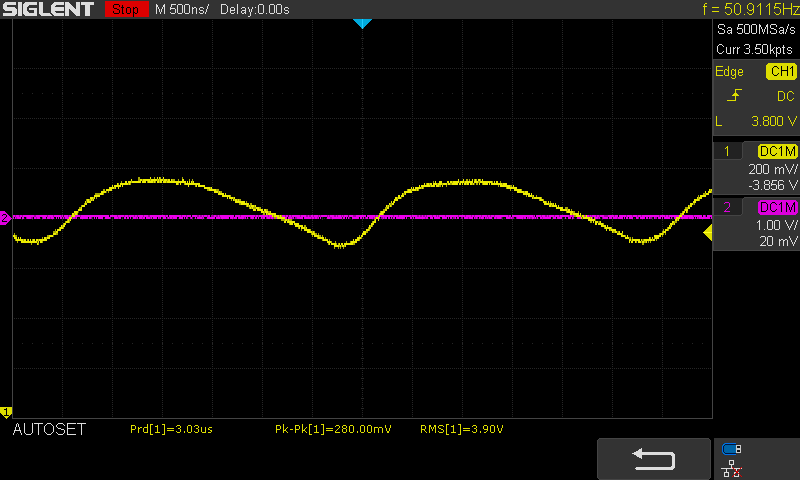

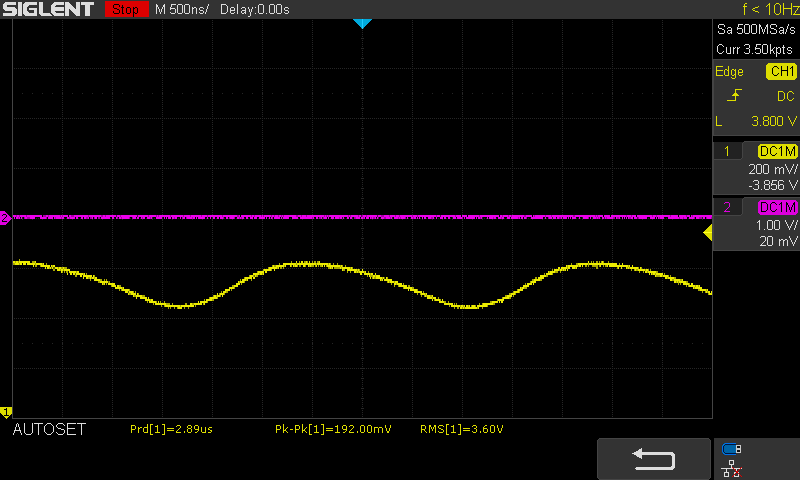

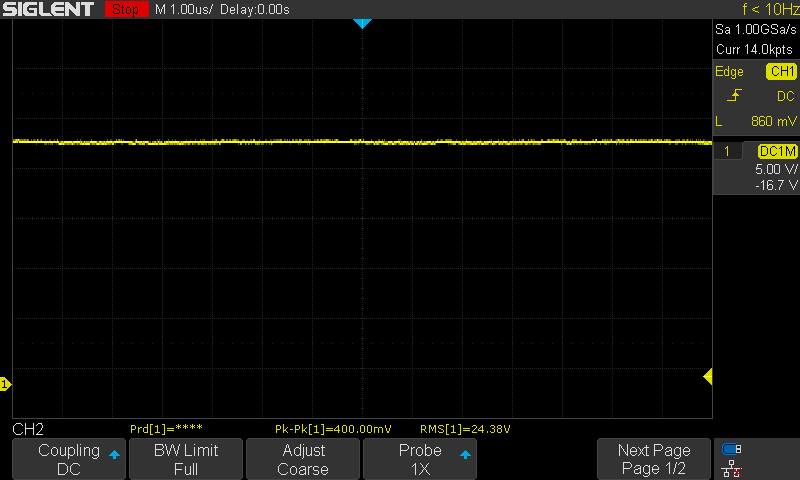

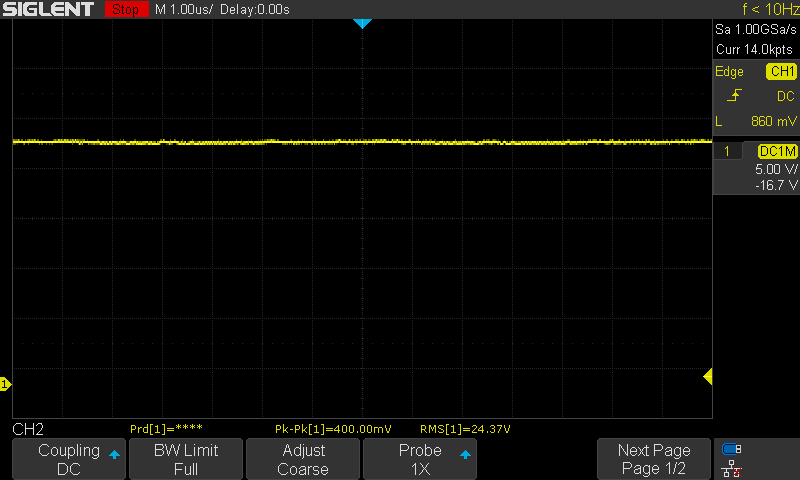

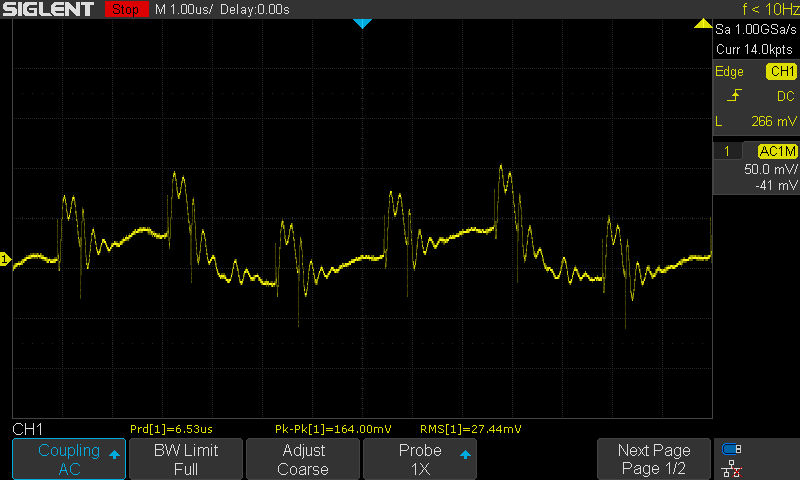

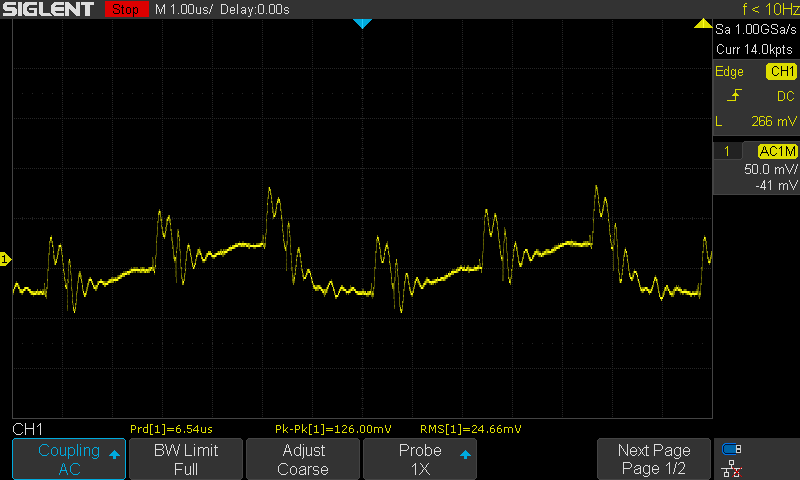

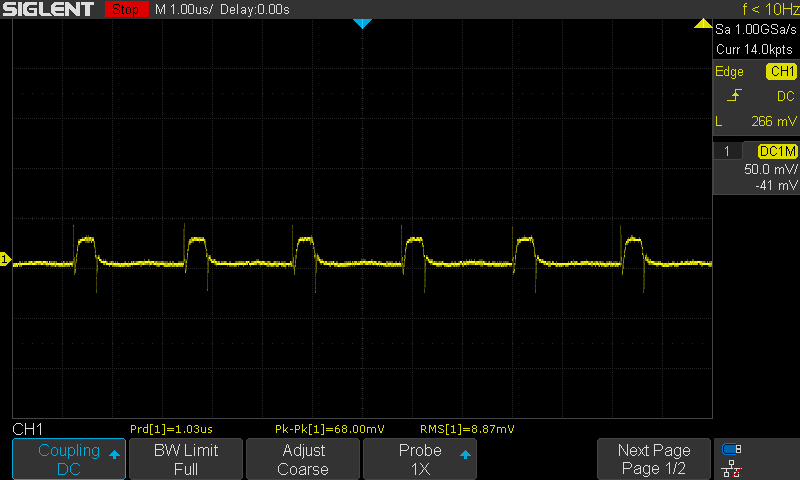

Under test, both the output voltage and the output voltage ripple increase steadily with input voltage. When supplied with 24V those values become way to high, for example up to 4.1V RMS and nearly 400mV peak-to-peak in case of the 3.3V regulator.

(Note Ron increased from 75k to 100k on this test, which didn't exactly help)

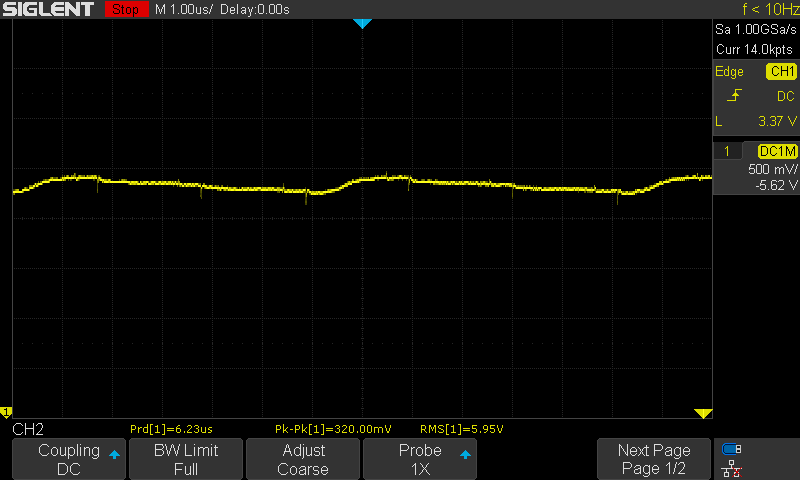

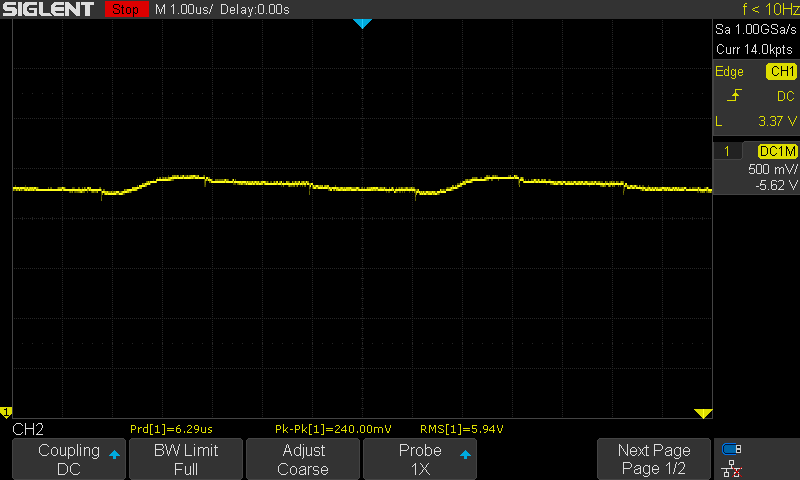

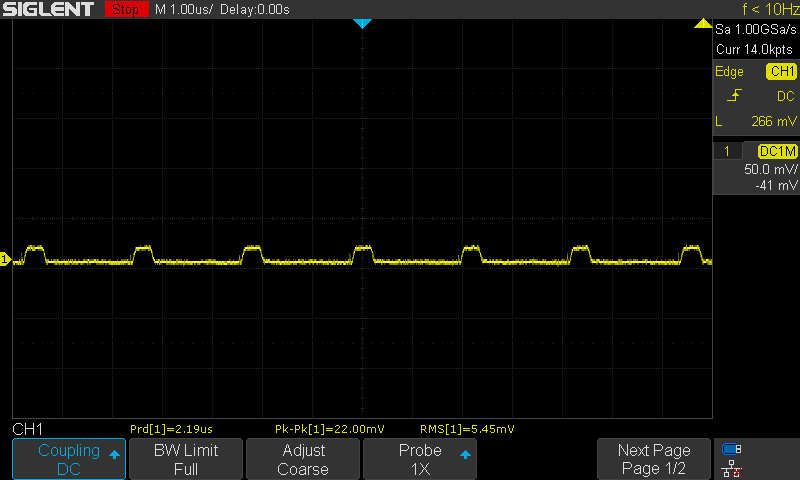

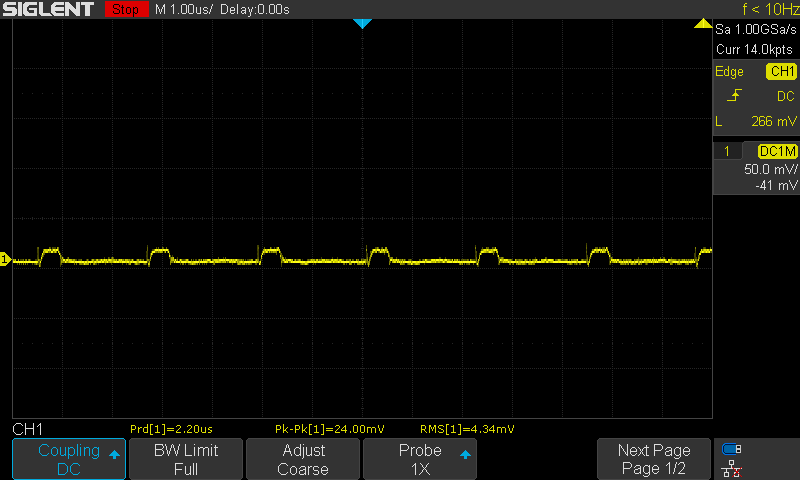

Increasing the inductance to 10uH and removing Cff (560pF appears high, compared to the example from the datasheet) reduces the symptoms somewhat. Adding load (2Ohm wire wound resistor) didn't change things much.

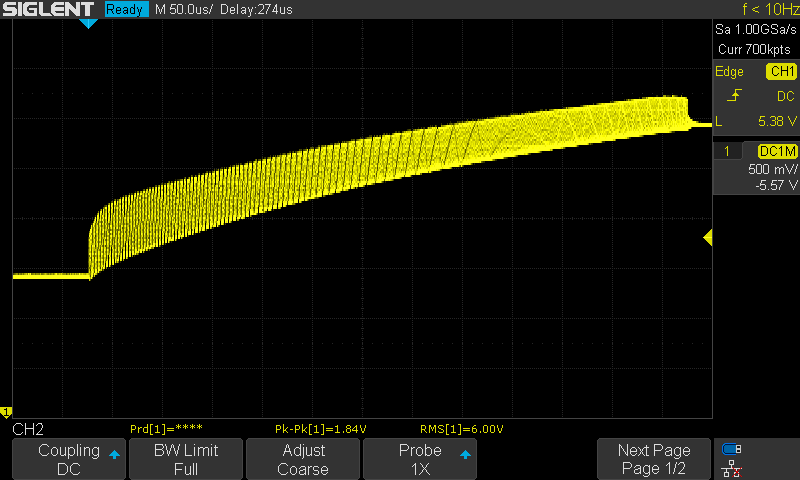

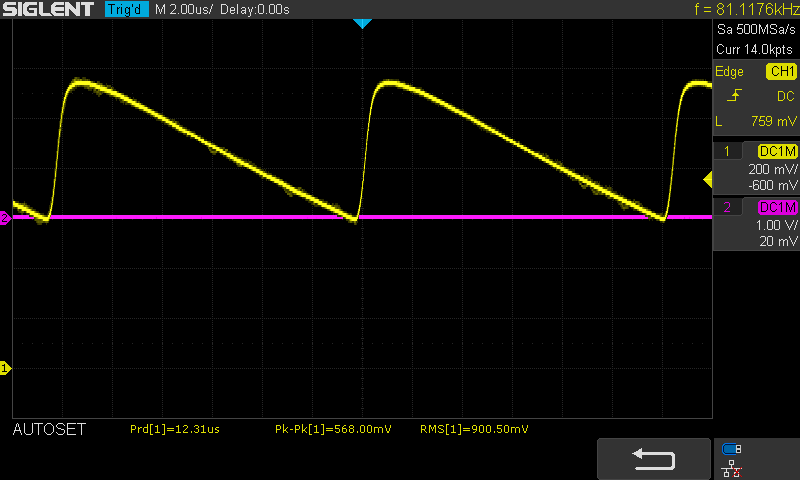

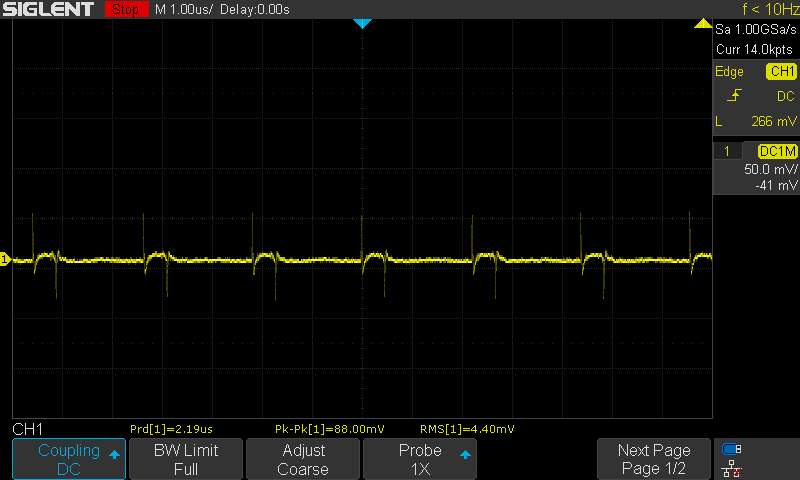

Another particular issue is the 5V regulator. It appears to be running in a discontinuous mode with short periods of switching ending in a too high output voltage followed by a decay to the nominal value over about 1 second. The other regulators don't exhibit this behavior.

As of now, I'm out of ideas what to try next, so any help is appreciated!

Best Regards

Reinhard