Hi,

I am using the UCC28180 for a 100V 3.5kW PFC converter with LLC. The application is audio amplifier. For continuous sinusoidal amplifier output of up to 3.5kW I have no problem with the controller and its operation.

However, when we apply burst mode tests where 2-4 cycles at 500Hz with powers greater than 8kW is applied followed by a continuous sine at a much lower level, the input current rises significantly higher causing the FETs to fail. Using the SOC and PCL control within the IC seems useless as the ICOMP saturates resulting in a high current spike on top of the sinus waveform, which causes failure of the device too. This seems to be a known problem having read on the forums, so I have set the limits much higher so it doesnt interfere.

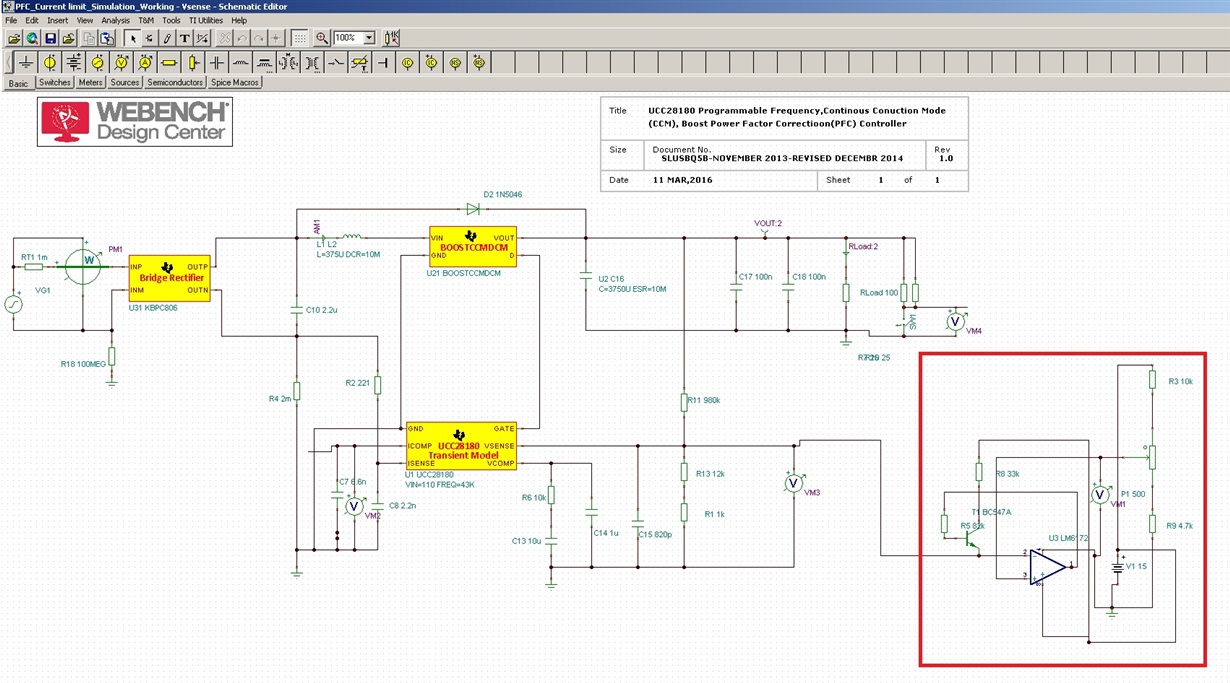

I am looking to implement a current limiting circuit externally where the I disable the PFC by shorting the Vsense when the current is higher than a set limit causing the output voltage to drop and enables once the current reduces below a threshold.

I am looking for some input into any circuits which have been used previously to perform this function. Alternatively, your opinions on whether or not this is a feasible solution would be very helpful.

In the image below CH4 is the output signal of the amplifier, CH2: is the PFC input current, CH3 is the resonant converter current. At present I am using the current limiter on the resonant converter, but it doesnt seem to be the best solution as it affects continuous power operation.

Without current limiting of the resonant converter the input current looks as below.

Thanks

Pravin