Other Parts Discussed in Thread: UCC2895, , TIDA-00778

How possible is it that UCC HO/LO Totem poles reversed design require inverted PWM on HI/LI?

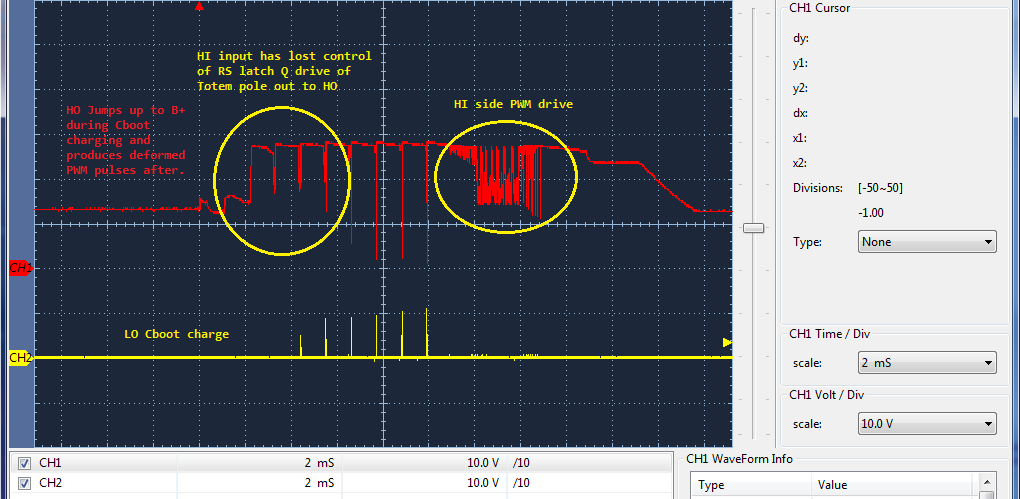

We used same application firmware with top gate driver over past years and not had such PWM issues as with UCC. We can not get UCC B phase PWM to transition onto either side or back to phase A or C phase. The B phase LI seems to disrupt HS/HB discharge of Cboot path and drive inverter voltage very high above DC supply stopped by MCU over voltage faults.

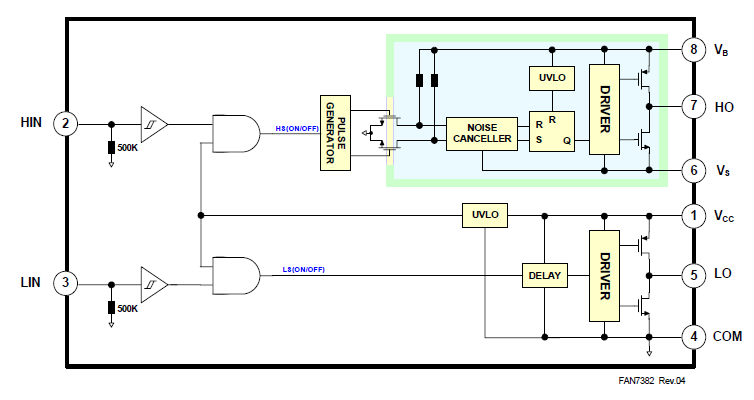

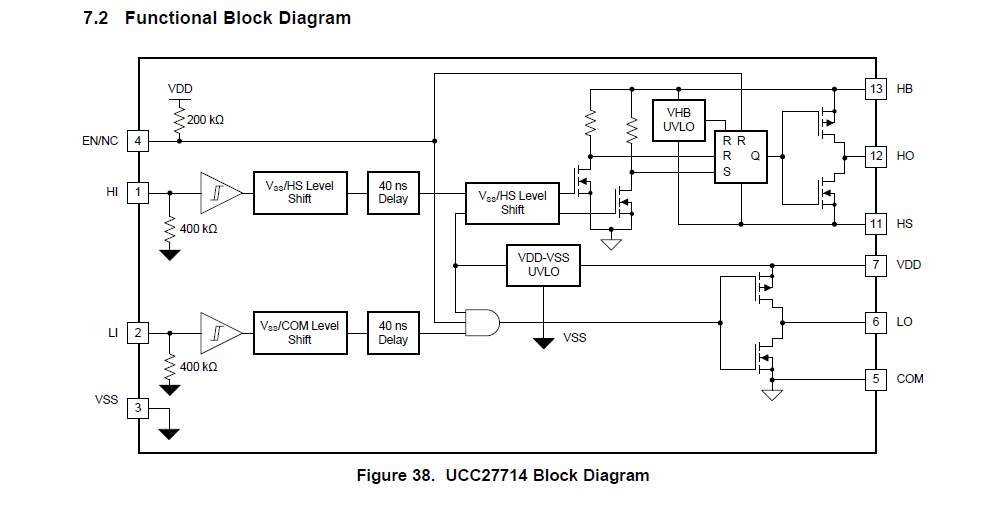

Notice the HO/LO PFET is reversed on other vendors gate driver!