Hello all,

Our customer measured TPS65218 by using theirs EVM. When VIN is forced, DCDC3 is 0v to 0.7V, 0.7V to 0v and DCDC3 is ramped.

It's strange behavior. TPS65218 goes to ACTIVE mode with no issue. When INT_LDO is remained above 0.6V, strange behavior is occurd. When INT_LDO below 0.6V, strange behavior isn't occurd.

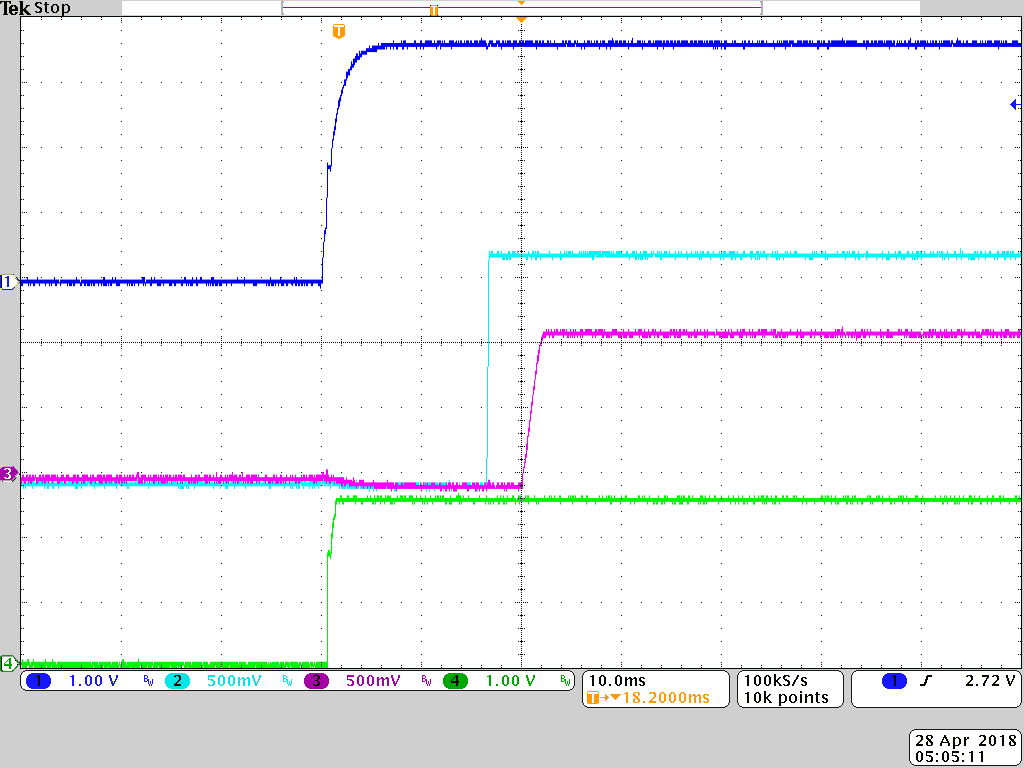

Is strange behavior OK? Or Do you have any solution? I attachied strange behavior  wave. CH1: VIN CH2: LDO1 CH3:DCDC3 CH4:INT_LDO

wave. CH1: VIN CH2: LDO1 CH3:DCDC3 CH4:INT_LDO

Best Rgards.,

M.Iwasaki