Hi

I have some question about current limit. It may be a basic question regarding to DCAP.

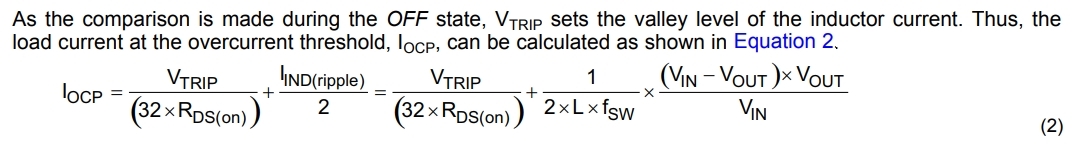

The current limit is comparison with IOCP set point during the OFF state .(Low side Fet is ON). It is a valley level of the inductor current.

On the other hand, it looks the top of the inductor current is compared at the following equation. ( IOCP= (VTRIP/(32*Rds)) + (IIND(ripple) / 2) )

Why the top of the inductor current is not compared but it is the valley of inductor current?

(Please correct me if my understanding is not correct.)

Best Regards,

Koji Hamamoto