Hi guys,

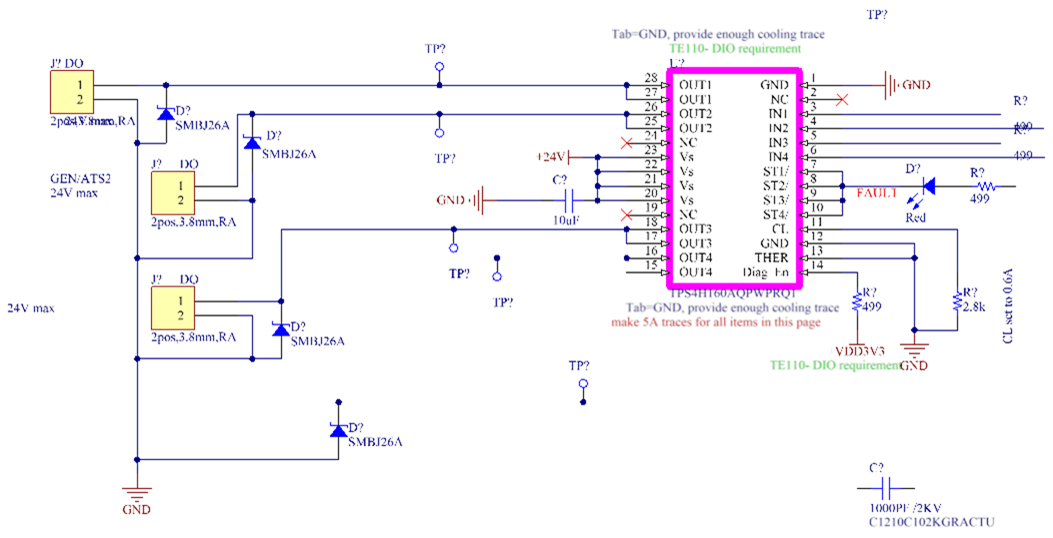

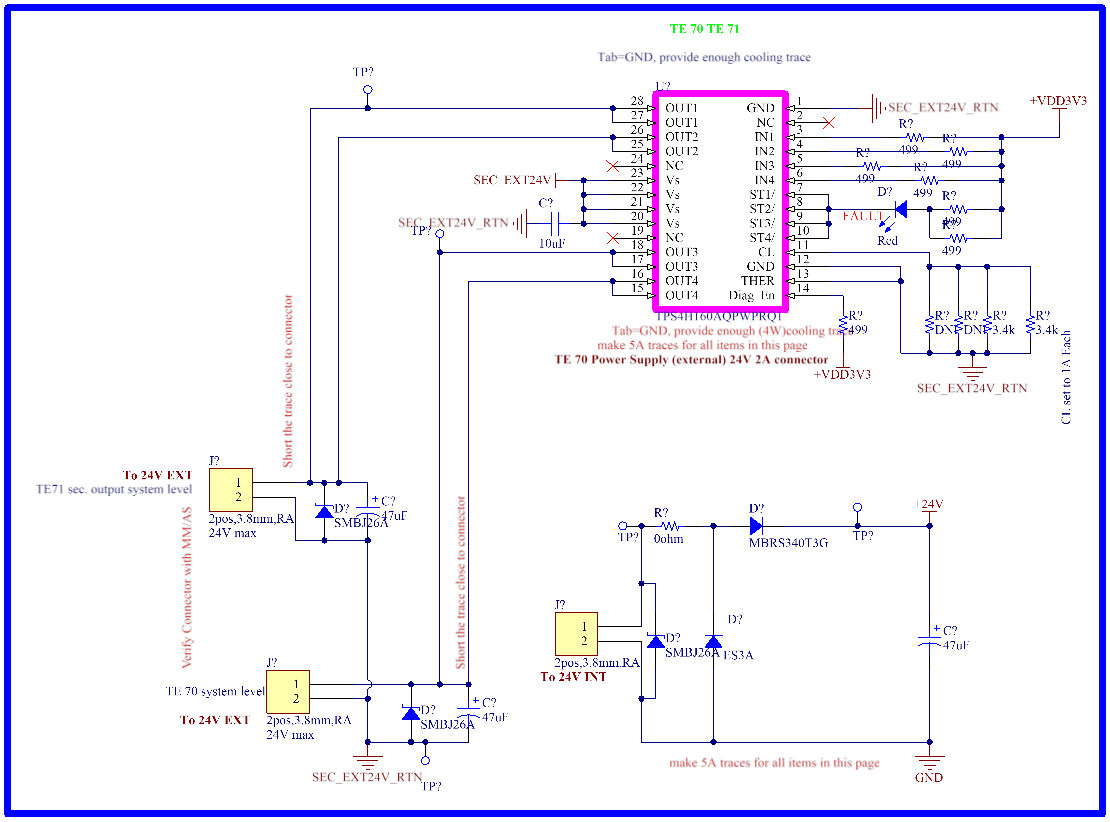

My customer designed in this high side switch and is having trouble with the parts overcurrent regulation. There are two cases and two schematic below, where one case operated as expected and the other did not:

Case 1: 2.8K Resistor was set for current limit of 0.6A but it did regulation/protection at 0.9A.

Case 2: 1.7K Resistor was set for current limit of 1A and it did regulation/protection at ~1A.

I am not sure why in case 1 it didn’t go good job of accurate limit but it did in second case.

|

RL [Ω] |

IRL [A] |

VRL [V] |

RCL [kΩ] (set for 0.6A) |

Mode |

Time [min] |

StS O/P [V] |

Device Temp. [⁰C] |

|

NA |

0.6 |

23.80 |

2.8 |

Ind. Config. |

NA |

NA-VerB |

NA |

|

NA |

0.7 |

23.76 |

2.8 |

Ind. Config. |

NA |

NA-VerB |

NA |

|

(29.65) |

0.8 |

23.72 |

2.8 |

Ind. Config. |

10min |

NA-VerB |

28.0 |

|

NA |

Drop from 0.9 to 0 |

23.40 |

2.8 |

Ind. Config. |

NA |

NA-VerB |

NA |

|

0(short) |

0A |

0.03V |

2.8 |

Ind. Config. |

NA |

NA-VerB |

NA |

Thanks,

Brian