Hi

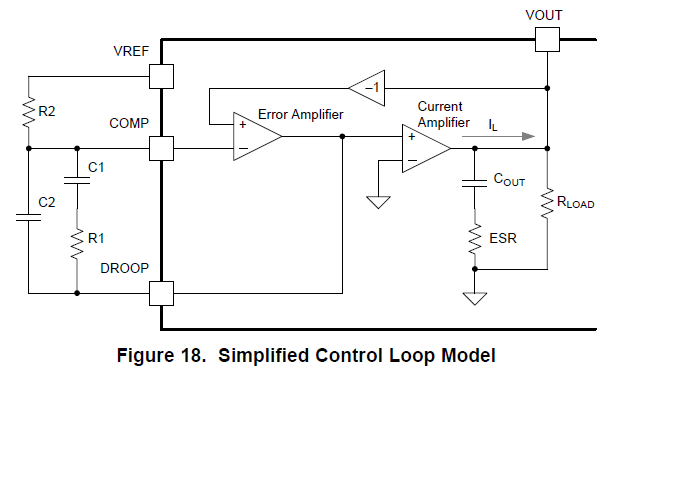

I use TPS54625 for my VRM to x86 CPU. I want to make loop statility test on tps53625. There is some info on page 37 of the datasheet about the control loop, but the test point about the loop stability test is not mentioned. Just like the figure blew.

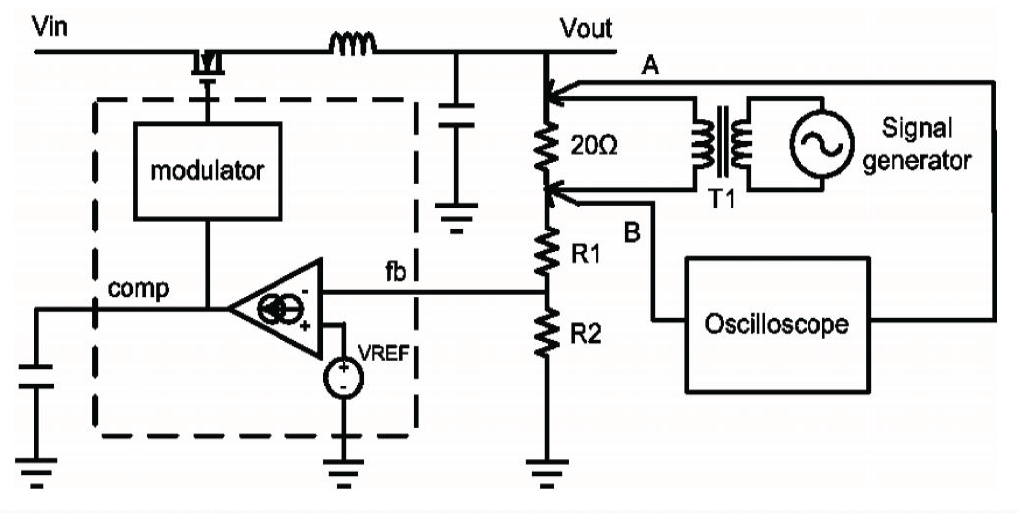

I want to know if I make loop stability test on tps54625, then my Signal Stimulus should be injected to where? As we know the test equipment usually have 3 probes (the signal stimulus, the input signal detect, the output detect signal) like the diagram blew.

Thanks!