Other Parts Discussed in Thread: UCC2895

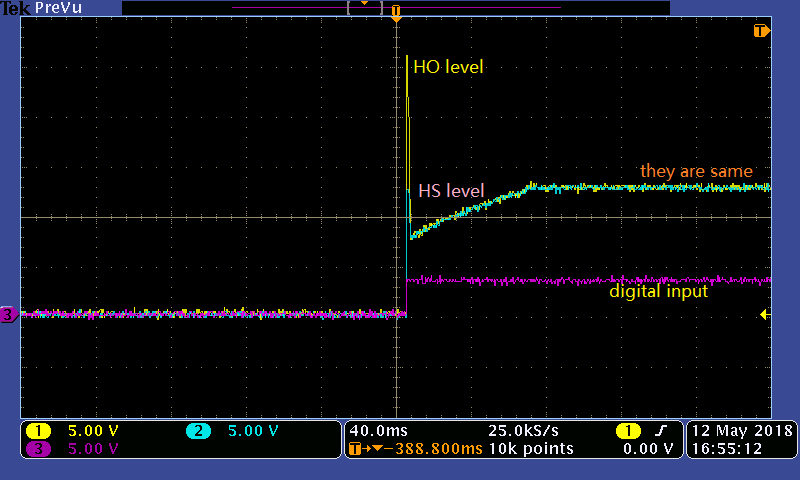

I bought some UCC27714 half-bridge driver to make a piezo high voltage driver few weeks ago.In my testing period, I encountered some problems. One is that the HO output is abnormal.

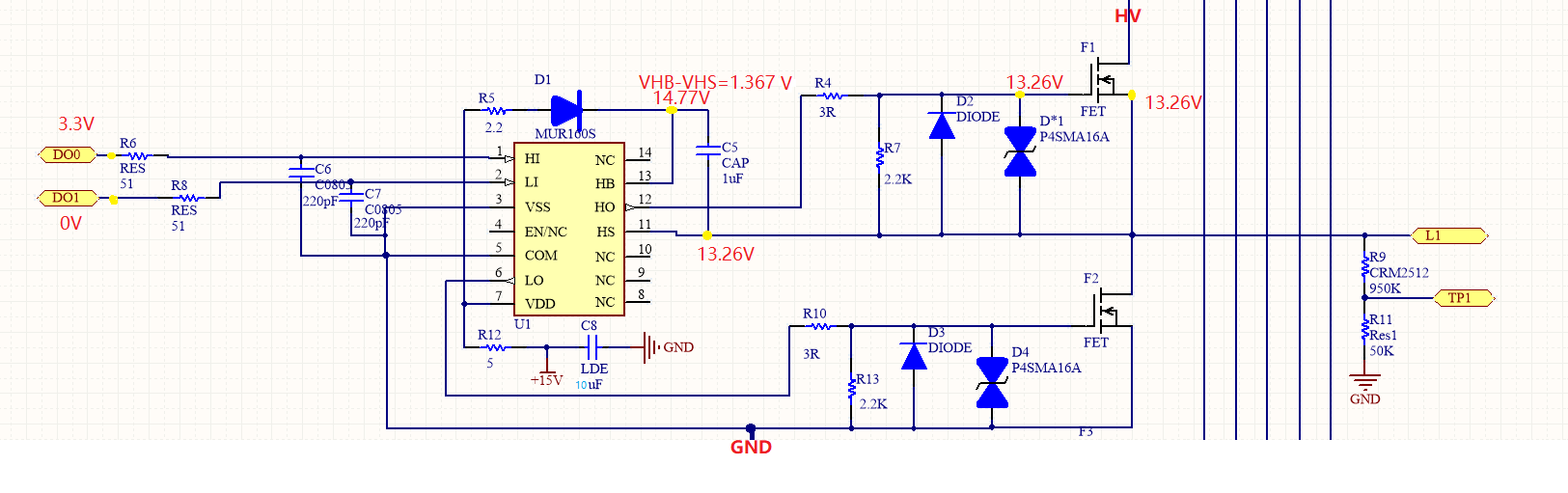

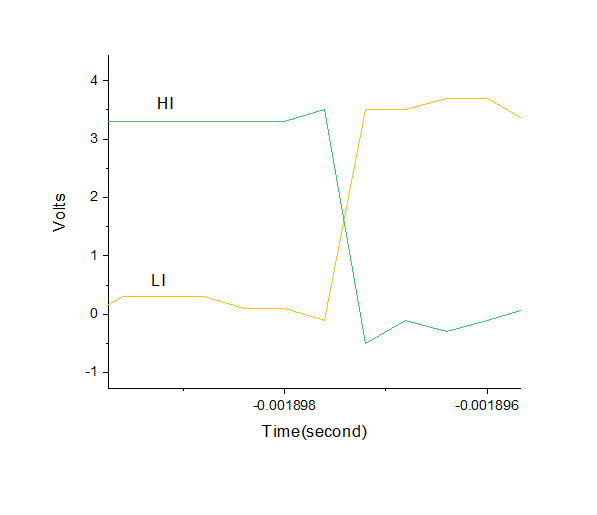

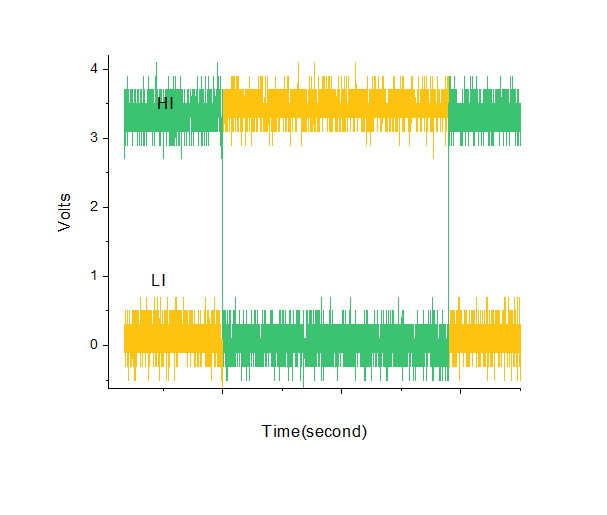

If I give a period rectangular wave that is HI and LI change from 0 to 1 periodicly. I find that the LO response is right. But the HO response is always the Vgate(Voltage on the FET’s gate pin) is equal to Vsource(voltage on source pin).My diagram is like this:

The yellow points represents test points. The red values are the tested values. I think this is UVLO fault. But I don’t know how to solve it.

Please give some tips. Thank you very much!