Hello,

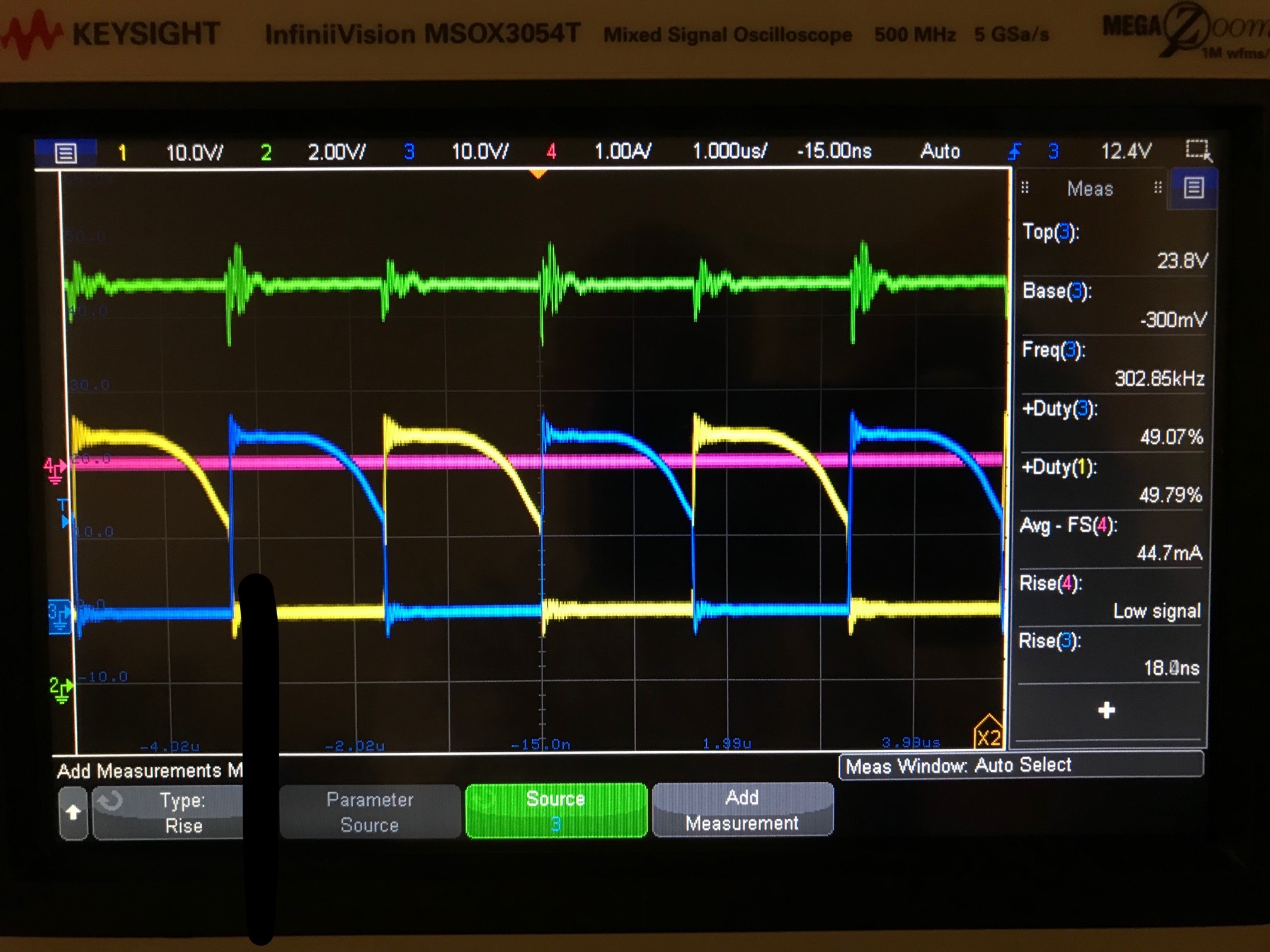

I have a TPS28225D on a board in a full bridge application. I am driving Qty:4 IRFR7446TRPBF MOSFET with a 5%-95% 300kHz PWM into a 0.25-2ohm load. I am currently have a problem that seems as though the gate driver is depleting its charge and dropping off after 1us at 24V. The feedback buck resistor and capacitor were initially 2ohm and 0.1uF. I then changed the the feedback loop to 0ohm and 0.22uF hoping it would add additional charge to sufficiently drive the gate. This was not the case. What might I be over looking to make sure my gate is fully driven for the full PWM cycle?

Image 1 (300Khz - 50% Duty Cycle, IRFR7446TRPBF (CASE1 - Simple Droop))

Image 2 (300Khz - 50% Duty Cycle, STD25N10F7 (CASE2 - Droop with recovery)

Image 3 (A Side Driver Schematic)

BLUE - High Side A @ T56 (Phase A)

YELLOW - High Side B @ T73 (Phase B)

PINK - Current into 2ohm

Thanks,

Darnell