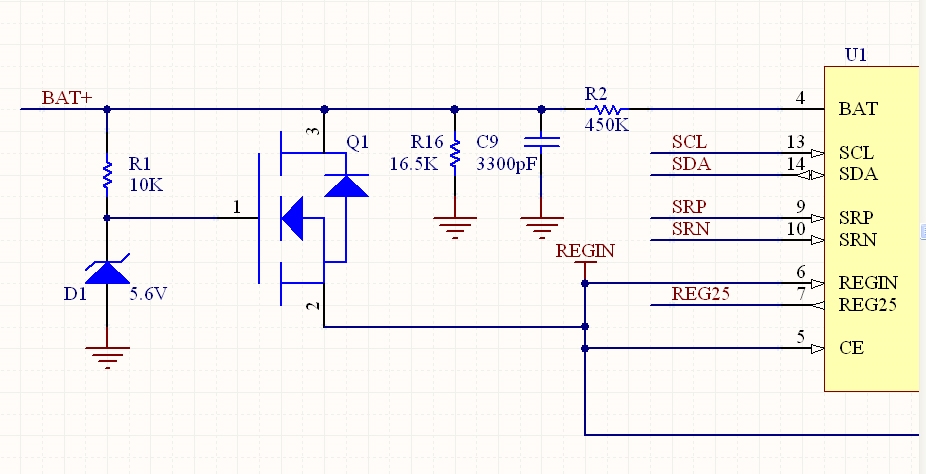

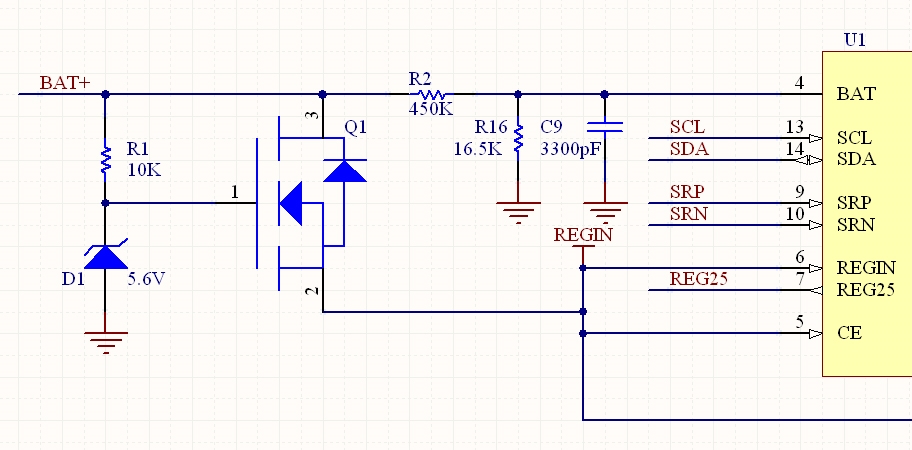

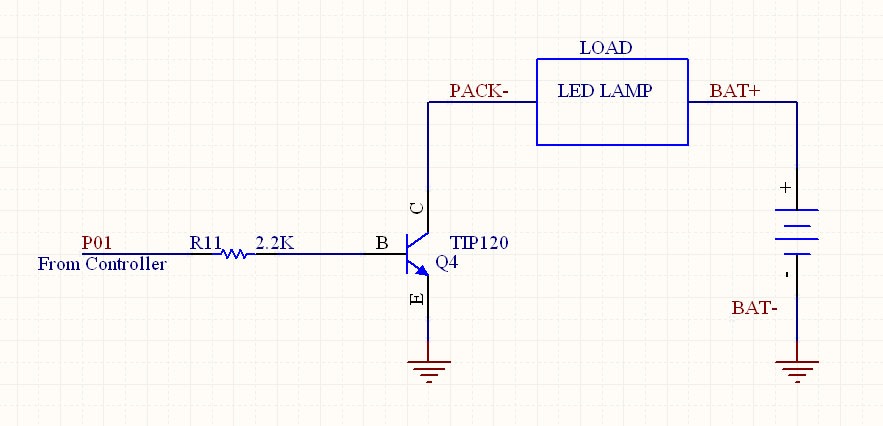

Other Parts Discussed in Thread: BQ34110, BQ77905, BQ7718

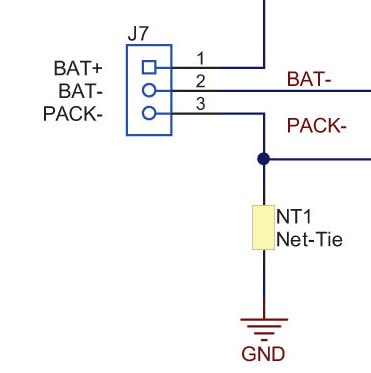

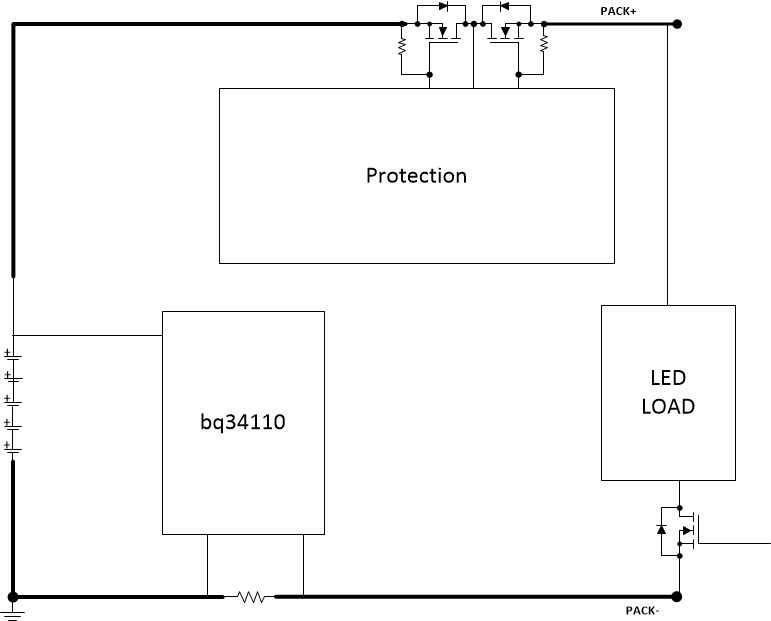

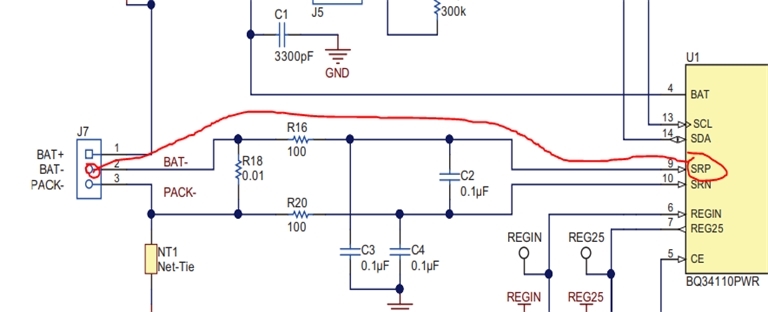

I'm trying to understand every detail of BQ34110 design based on the BQ34110 EVM. I still don't understand what J3 is used for. In the BQ34110 EVM user's guide (SLUUBI1), section 3.2.1 said that J3 is used to select the mode of operation, but doesn't explain any further. So I wonder which mode is it about?