Other Parts Discussed in Thread: TIDA-00778,

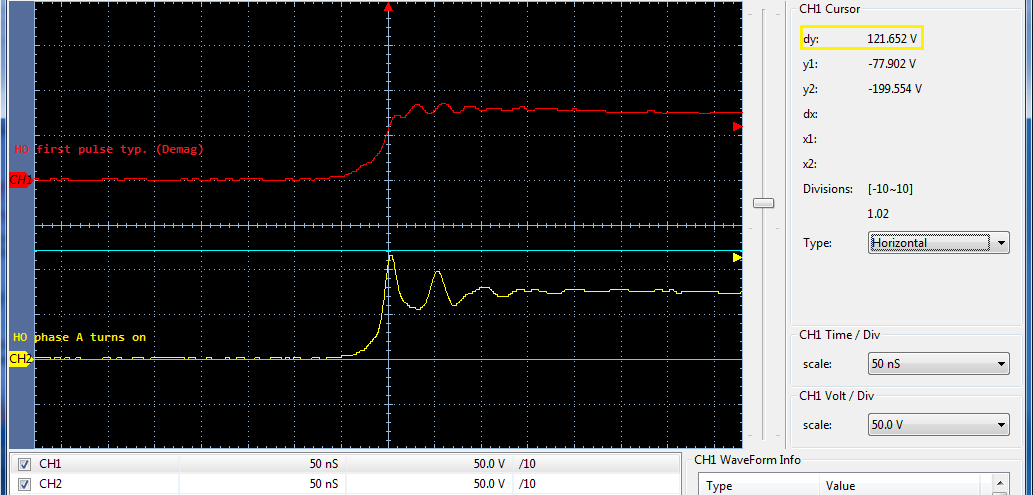

How can we without further increasing gate turn on/off resistance slow down HO rise to miller plateau to reduce NFET surging IAS events?

Can Cboot value directly impact the NFET QD-nc in such a way HO is to fast thus driving BVDSS excessively high? Perhaps the HO Totem pole enhancement (PChannel assist) can impact high side NFETS in a bad way too. Noticing HO driven DS rise time <50ns to Miller plateau and <100ns in first pulse often rising well over BVDSS source voltage. Example; NFET with 24v BVDSS is randomly producing well over 45v IAS peaks, not a safe condition. That NFET QG=89nc yet 24R/24R ohm gate drive can compromise HO output with higher BVDSS source 80volts recently tested.

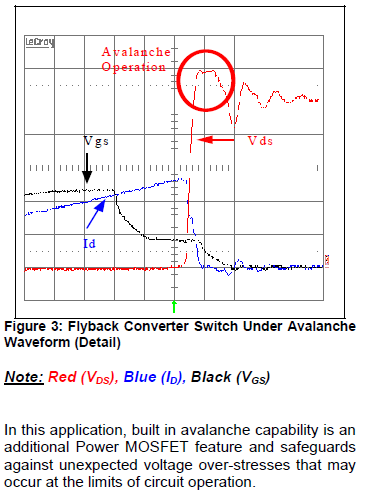

Might Rboot/Cboot RC time constant values chosen for typical industry gate drivers, with UCC effect NFET in driving excessive pre-mature IAS events? Otherwise what is the purpose for +/-IGPK 4 amp <10us PW if the HO output is easily compromised with typical Rboot/Cboot RC time constant often chosen for lesser speed gate drivers? The idea in my mind is faster UCC HO slew rate ability needs to be regulated for soft start boot charge cycles, not simply push the Miller plateau and drive IAS events in the process. The ringing often occurring after the Miller plateau according to Infineon is an IAS event not necessarily caused by stray parasitic.