Hello,

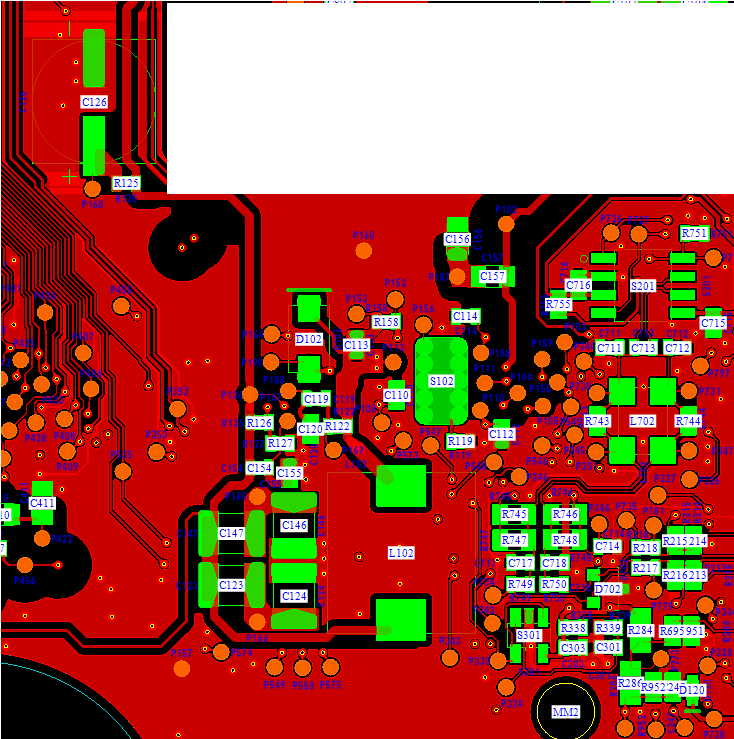

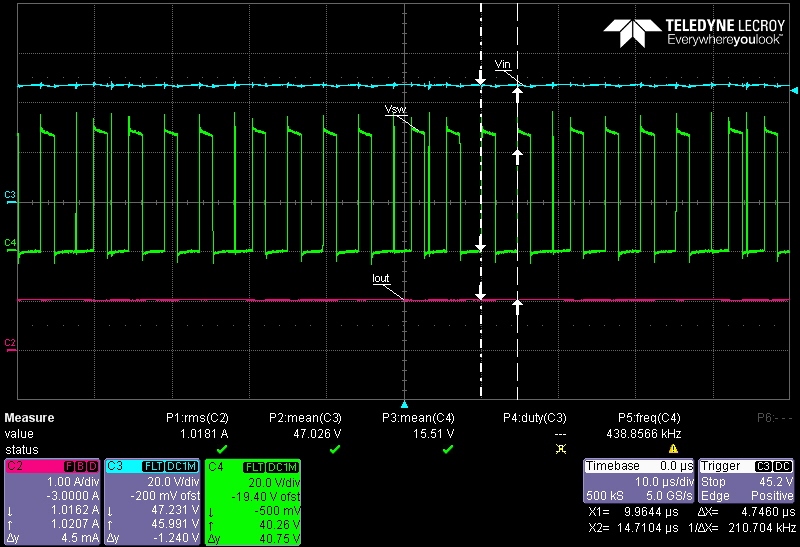

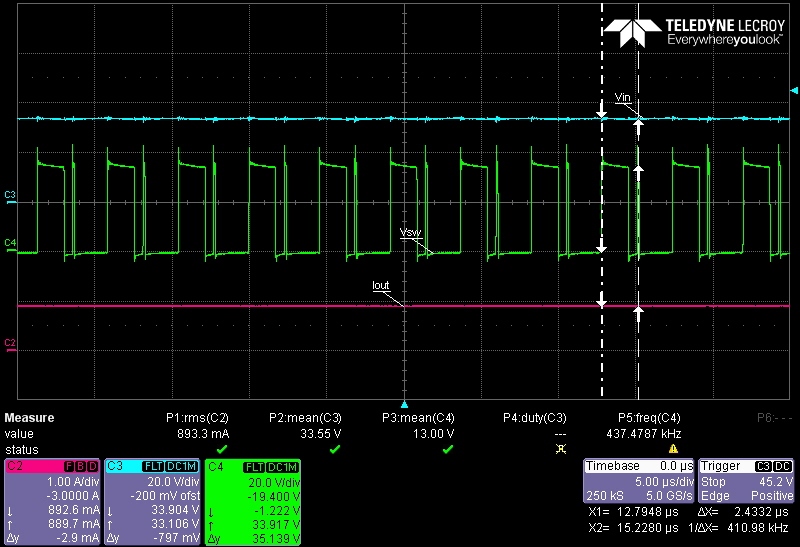

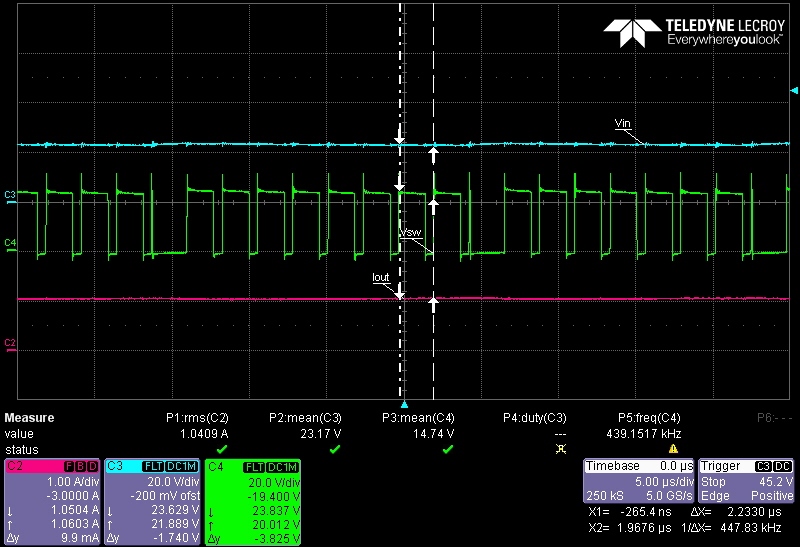

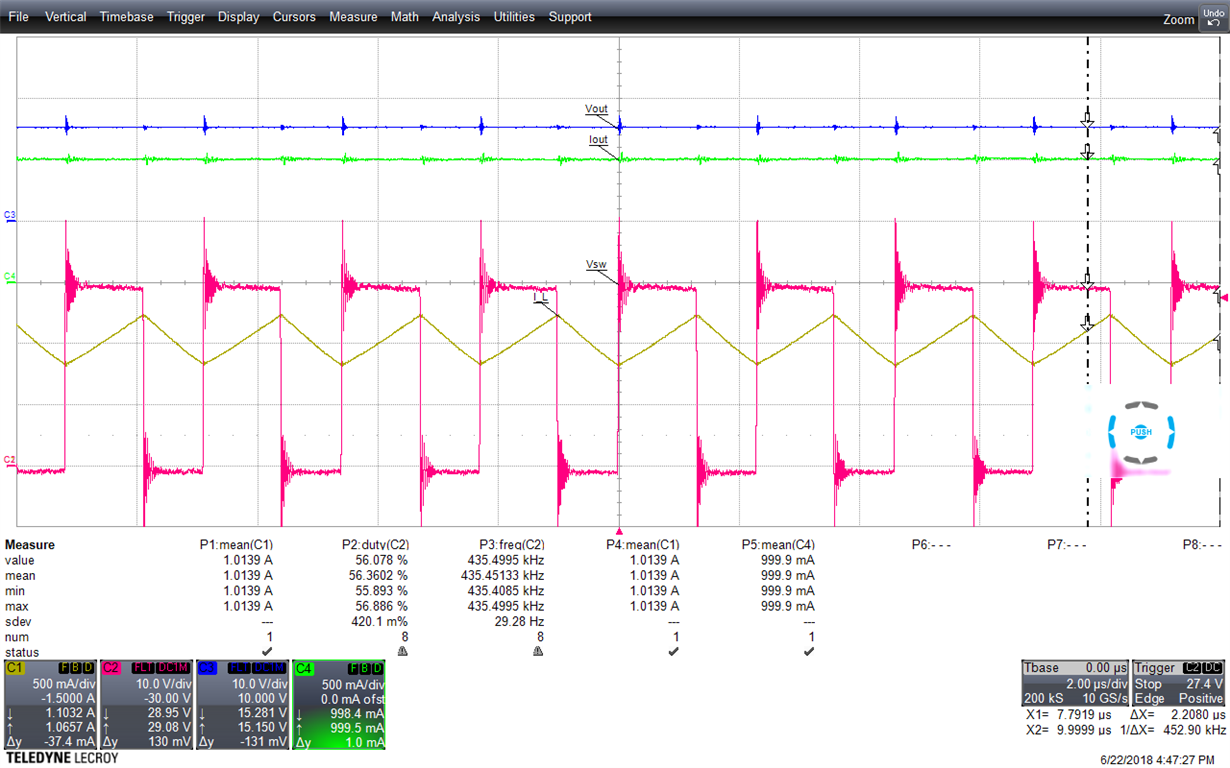

We have implemented DC-DC buck converter to down-convert the 48V to 15V. During the Line regulation testing, we found an issue with the output voltage that not being stable for the whole range of voltages.

The schematic is designed for the operating voltage range of 24V -56V with a nominal voltage of 48V and load current of 0.8A. During the verification of the device, for the following test there has been a unintenteded observation made as explained below.

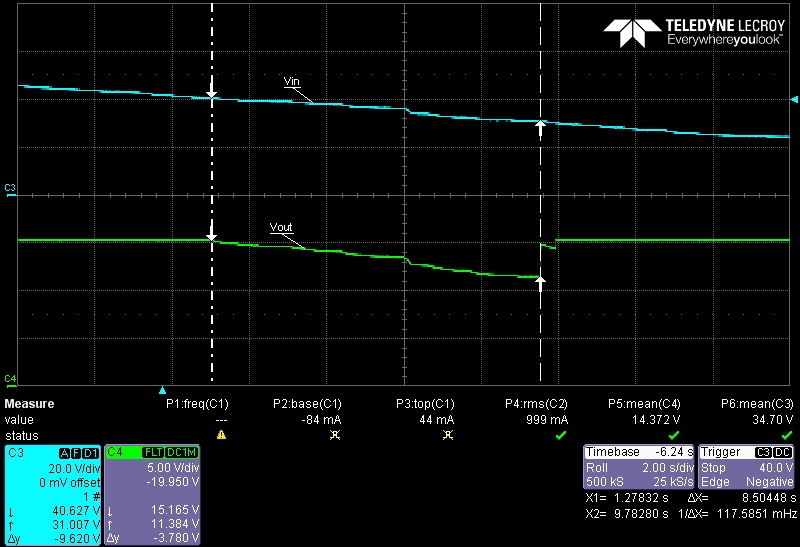

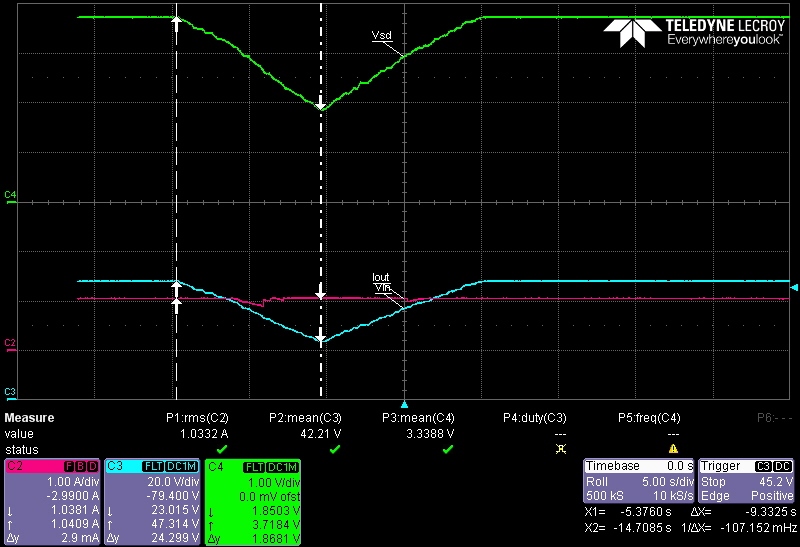

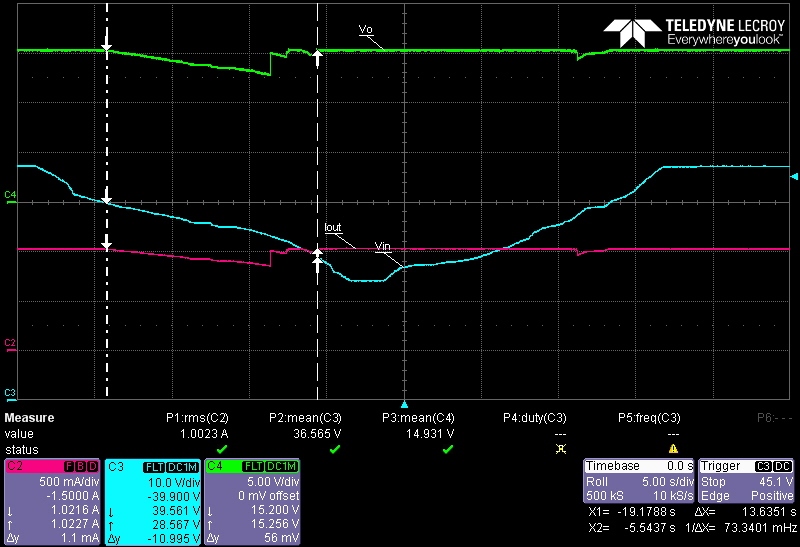

With a load current set to 1A, the input voltage varied from 48V to 25V. During this ramp-down, in the range from 40V to 30V the output voltage was deminishing slowly from 15V to 13V. This was unaccepted from the device.

Could you please look for some reason for this behaviour and get back to me with a feedback?Please revert if you need any additional information on the same.

Thanks.