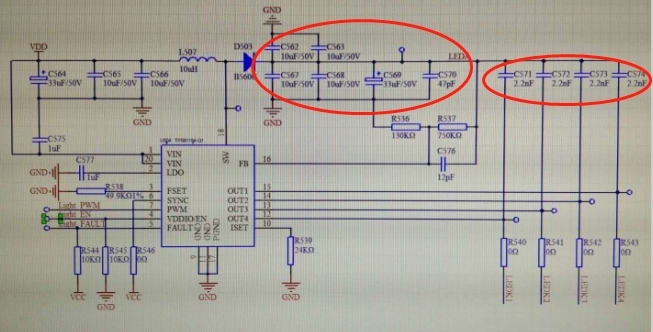

here is the SCH with layout:

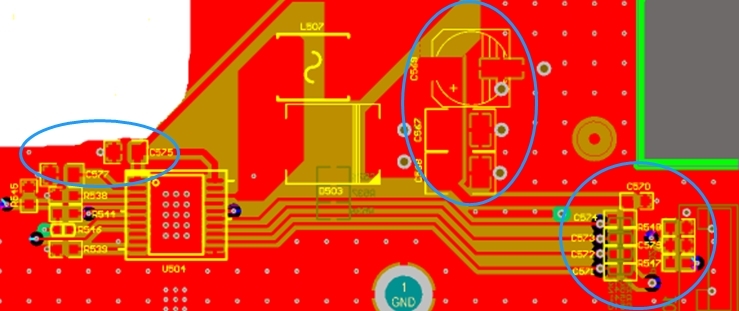

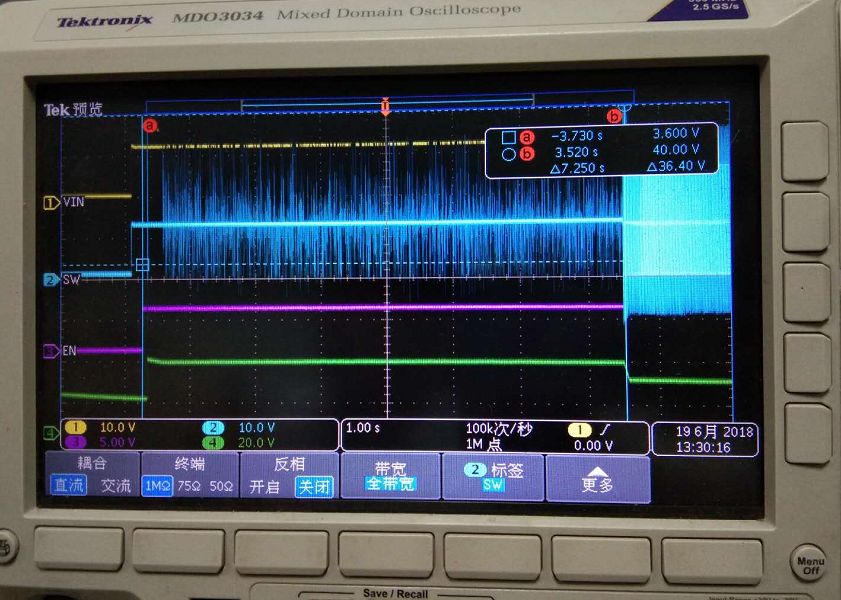

We tested the waveform of OK and Wrong:

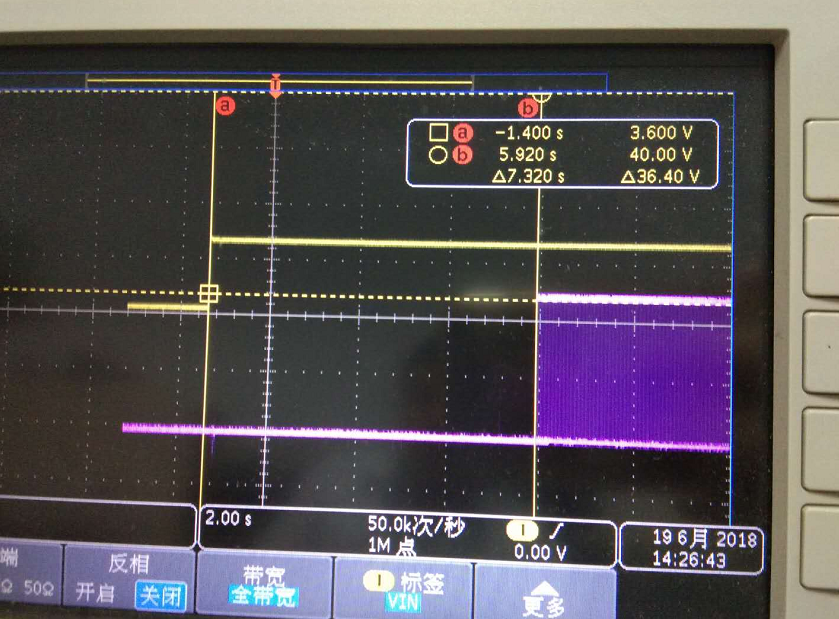

OK:

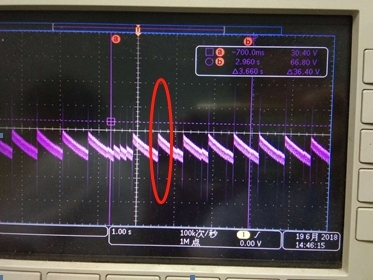

Wrong:

and test PWM to show the turn on timeline

Found it may be cause by peak of SW,and continue enlarge the wavefrom of SW:

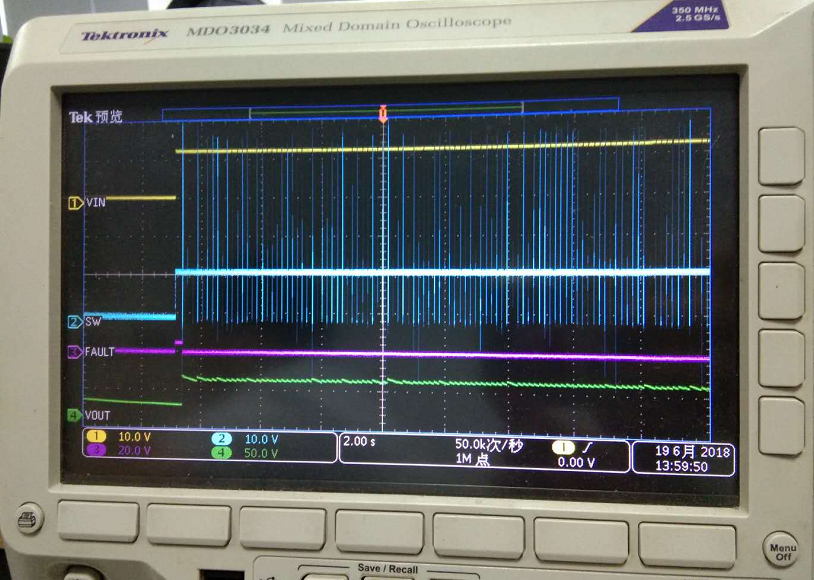

Then test the OUT1~4 of TPS61194-Q1

according to the datasheet:

Customer wonder if it is really cause by peak of VOUT,Then how to develop the SCH?There are some different Cap for this part,but still could not work well?

Or there is another reason?Customer want to apply for FA ,inorder to check the wrong in IC

Or wether it is decided by TPS61194-Q1 ?