Hi ,

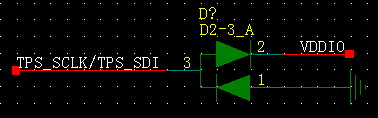

based on my customer's test, they use TPS65381-Q1 as power supply for TMS570 and they found there is negative spike on SCLK and SDI. Those SPI communication pins are connected directly between devices.

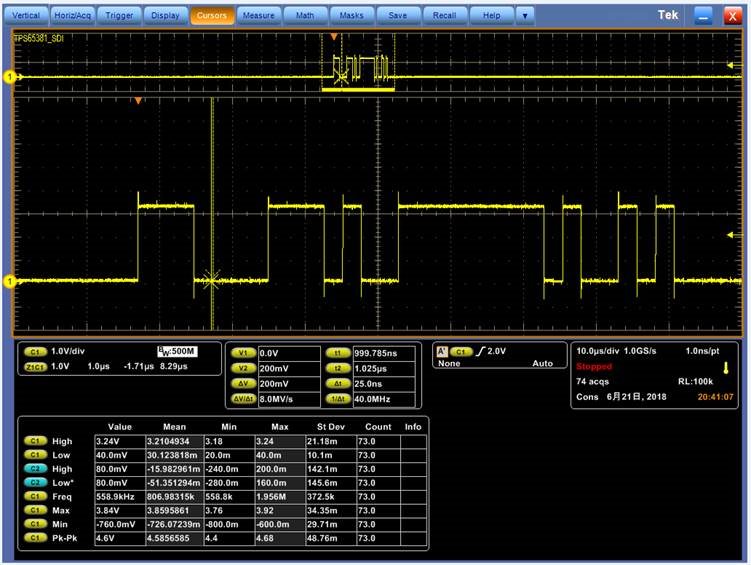

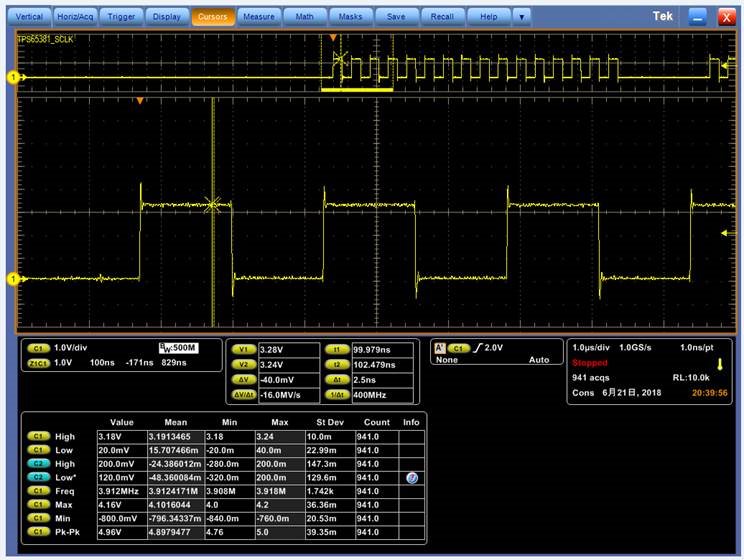

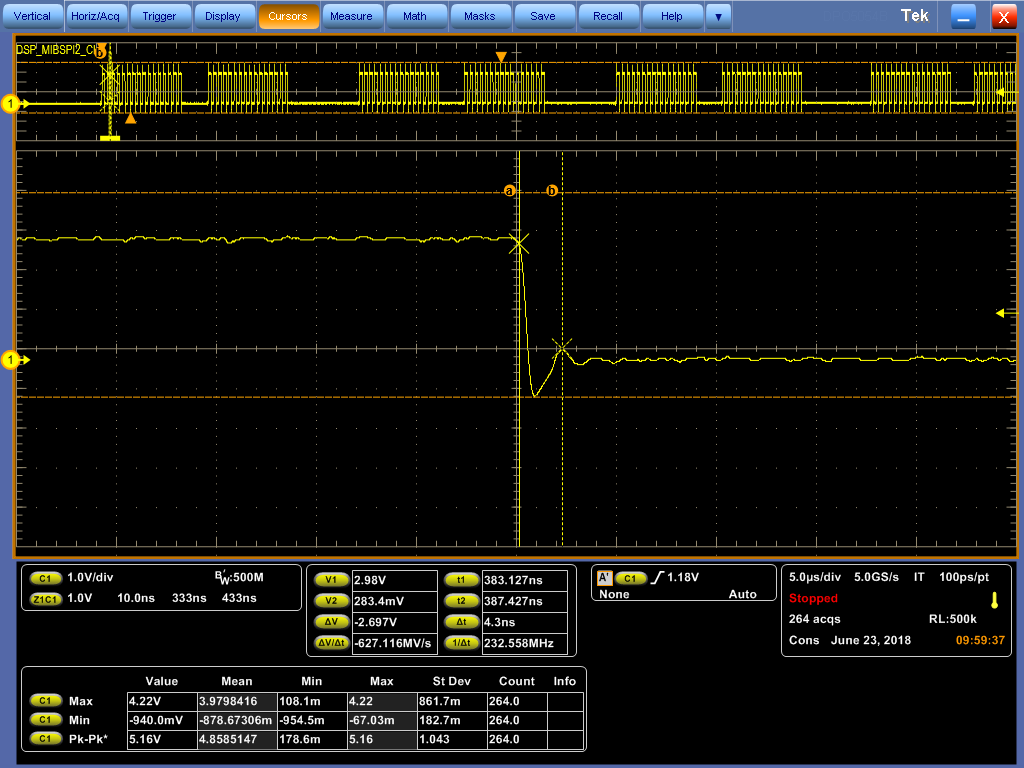

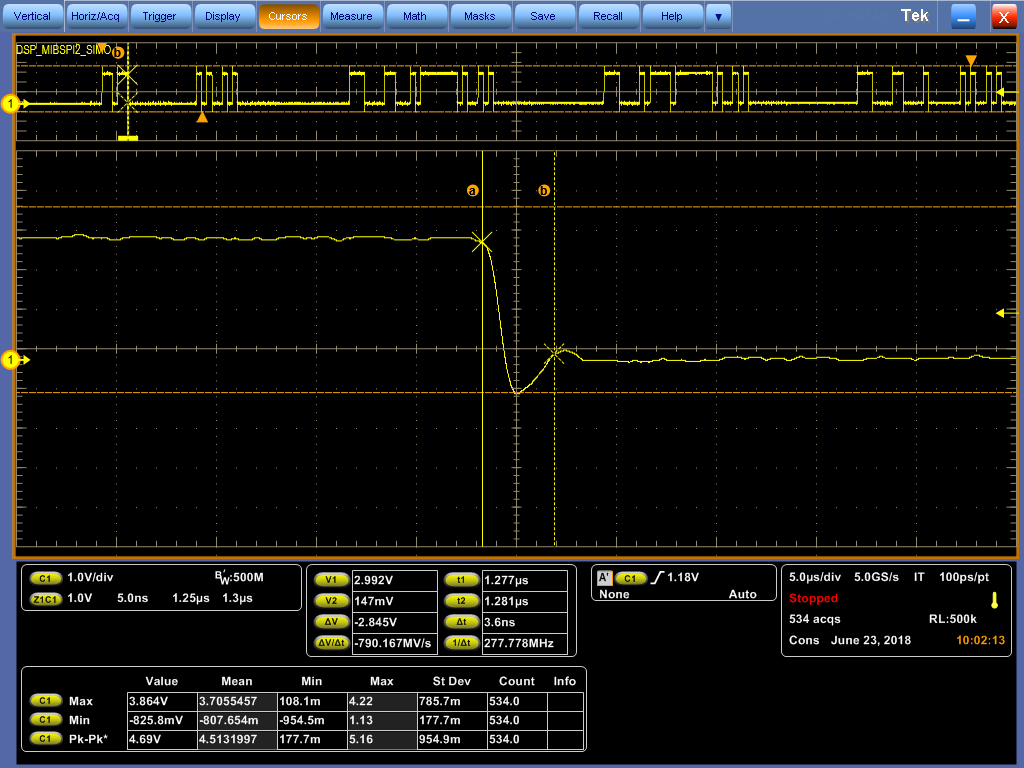

waveforms are as attached;

SCLK: -0.8V ( <200ns)

SDI : -0.76V ( <200ns)

Please kindly help check if -0.8V( 200ns) will damage the part since spec says -0.3V and if there is AC spec on this.

Thank you.

BRs

Given