Hi,

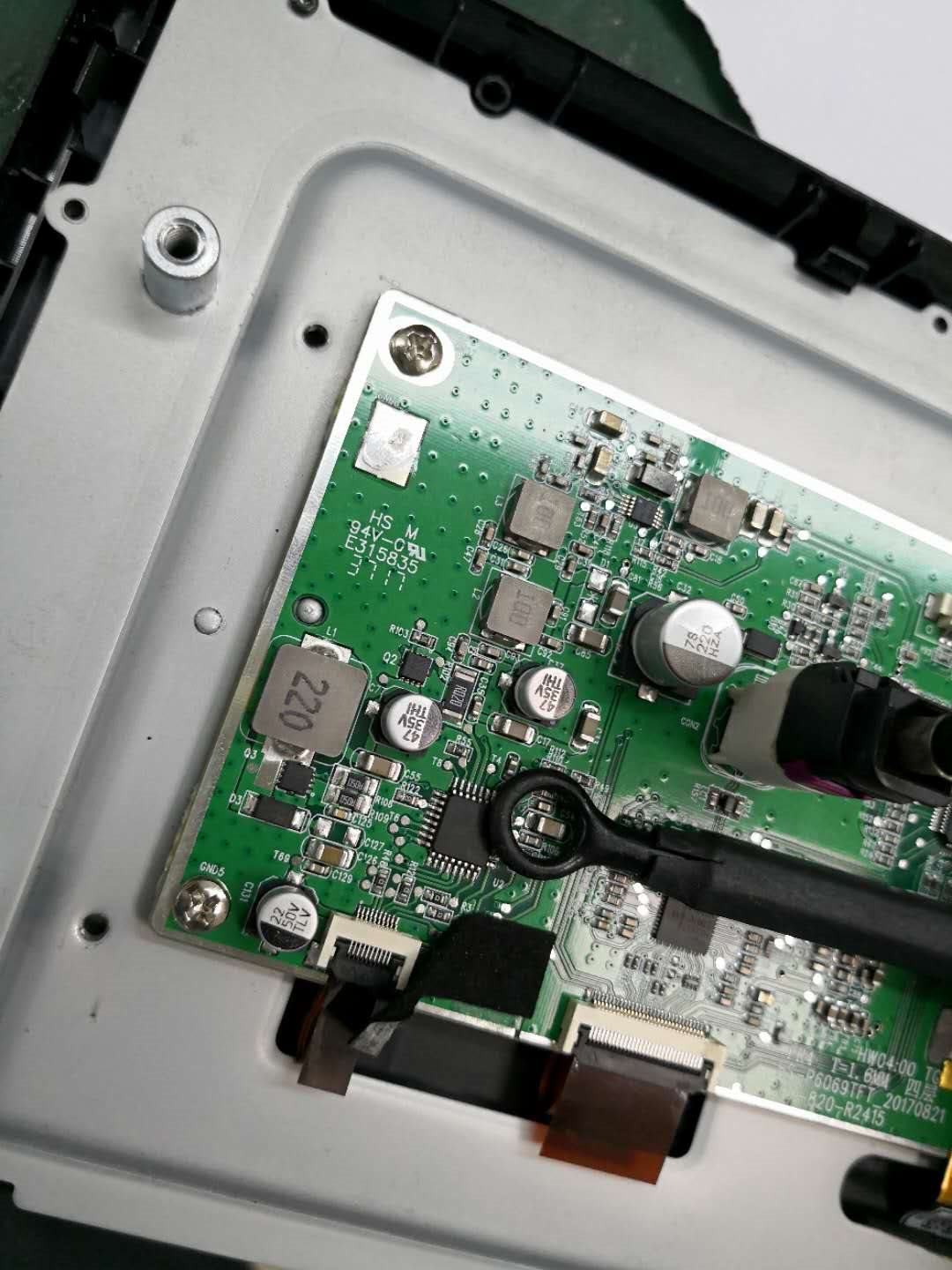

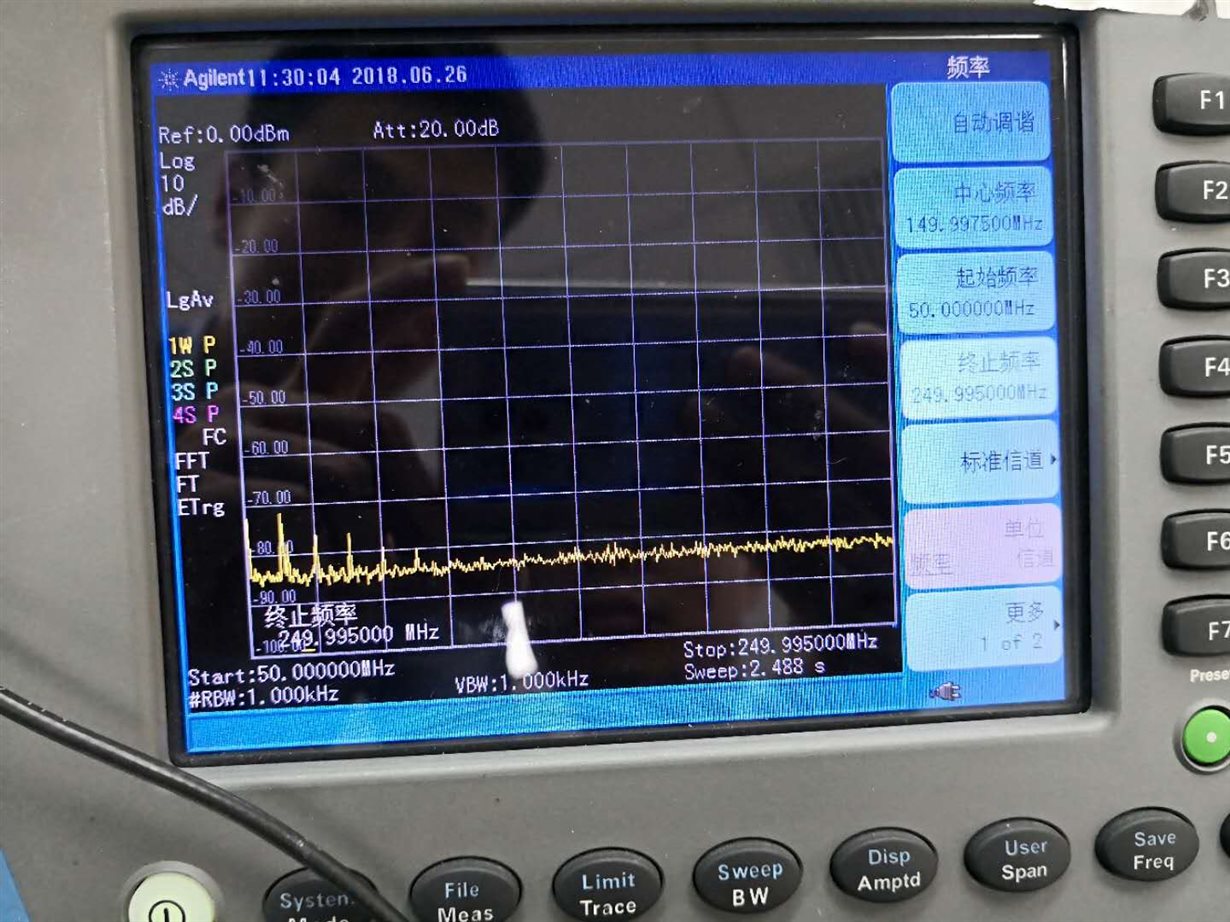

My customer uses LP8860-Q1 in one of their display modules, they failed the EMI conduction test in 80M/90M/100MHz.

I am thinking if there is something to do with LP8860 since it has a 10MHz internal clock which matches well the failed frequency. We use near-field frequency spectrum to test the LP8860, we do find the 10MHz peak frequency and its harmonics.

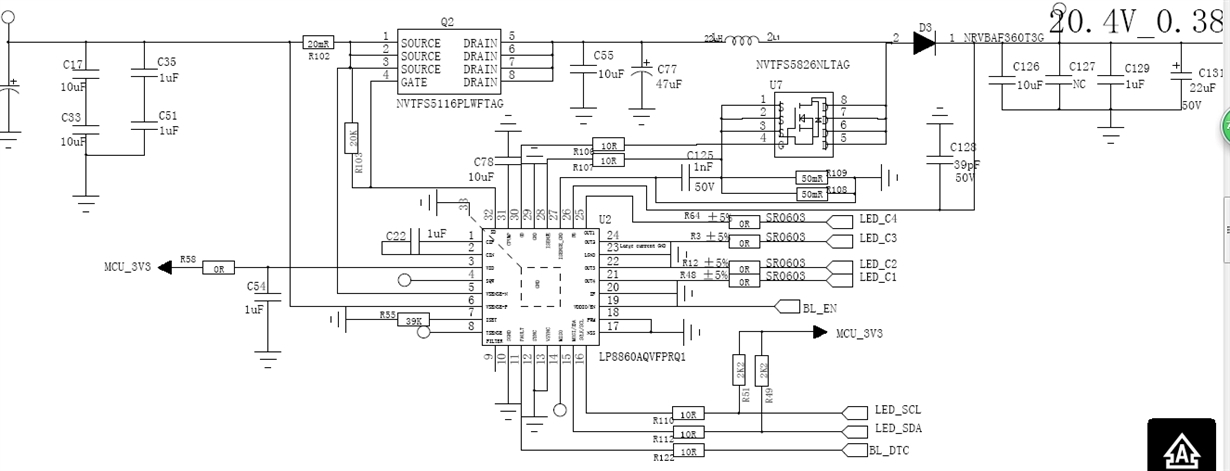

- I attach the schematic and eeprom, according to customer's setting, EN_PLL=1 and FILTER pin is floated, is that the root cause? Can we use internal 5MHz osc directly and disable PLL?

- Could you also double check the schematic and eeprom, what are the possible reason for 10MHz peak frequency?

- For the boost input and output capacitor, is that ok to use below value? what are the risks?

EEPROM reading:

(T8U)0x60,(T8U)0xEA,

(T8U)0x61,(T8U)0x21,

(T8U)0x62,(T8U)0xDC,

(T8U)0x63,(T8U)0xF0,

(T8U)0x64,(T8U)0xC7,

(T8U)0x65,(T8U)0xF5,

(T8U)0x66,(T8U)0xF2,

(T8U)0x67,(T8U)0x77,

(T8U)0x68,(T8U)0x77,

(T8U)0x69,(T8U)0x71,

(T8U)0x6a,(T8U)0x37,

(T8U)0x6b,(T8U)0xB7,

(T8U)0x6C,(T8U)0x17,

(T8U)0x6D,(T8U)0xFF,

(T8U)0x6E,(T8U)0xB9,

(T8U)0x6F,(T8U)0x87,

(T8U)0x70,(T8U)0xC9,

(T8U)0x71,(T8U)0x72,

(T8U)0x72,(T8U)0xE5,

(T8U)0x73,(T8U)0xDF,

(T8U)0x74,(T8U)0x35,

(T8U)0x75,(T8U)0x06,

(T8U)0x76,(T8U)0xDE,

(T8U)0x77,(T8U)0xFF,

(T8U)0x78,(T8U)0x3E

Best regards.

Dongbao