Hello, I am studying your LM5035 half-bridge circuit evaluation board. I want to mathematically model the half-bridge circuit on the evaluation board to write the open-loop transfer function of the power supply.

However, I can't write the model of the LM5035 optocoupler part. Because the output side of the optocoupler's transistor is a current signal entering the COMP pin of the LM5035, it is different from the conventional voltage signal entering the COMP pin of the control chip.

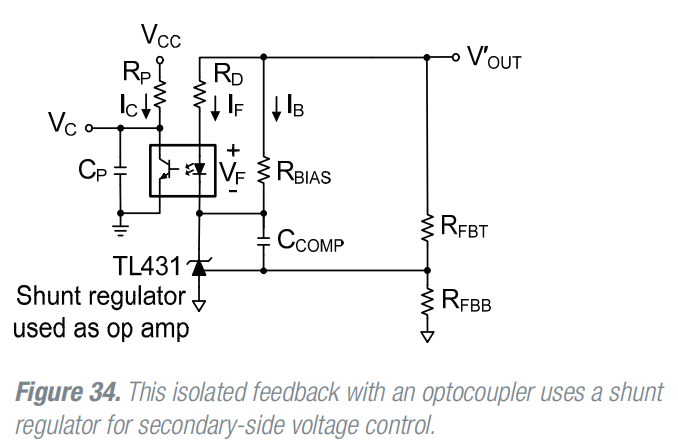

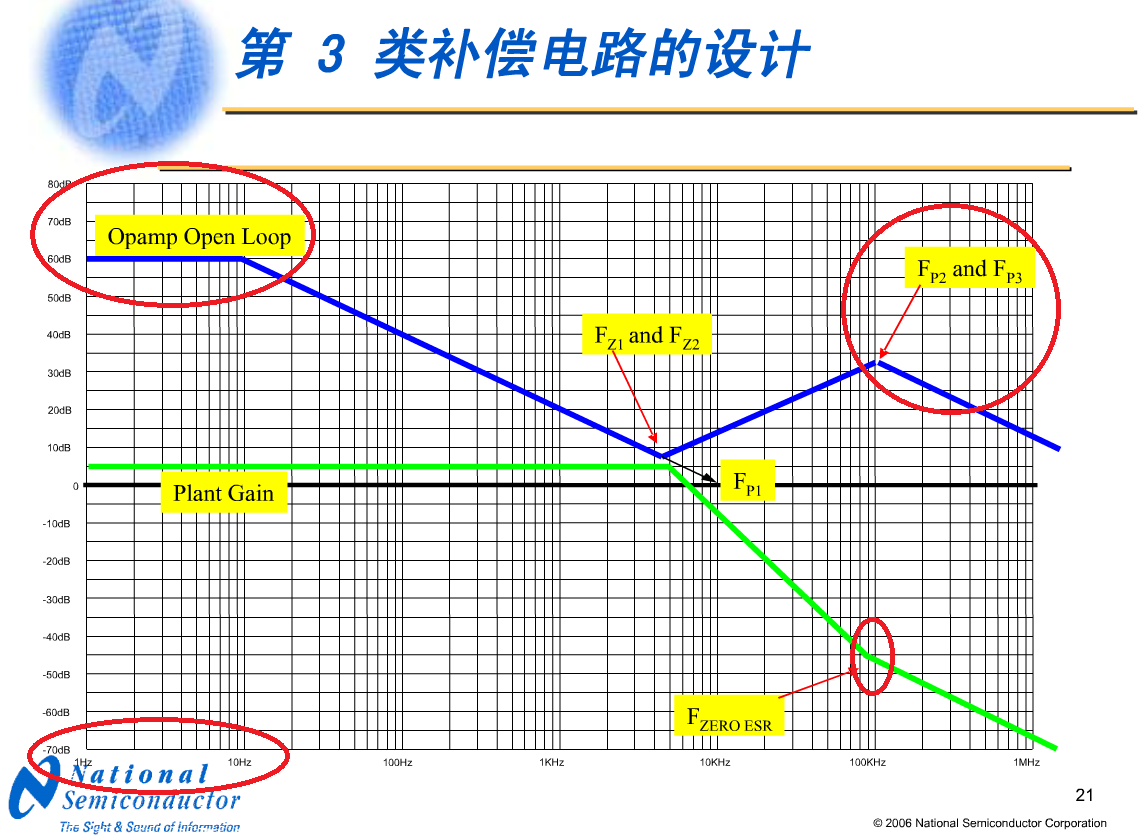

Refer to the 34th picture and the formulas 88 in the application report of "Switch-mode power converter compensation made easy" written by your experts Robert Sheehan and Louis Diana, as shown below:

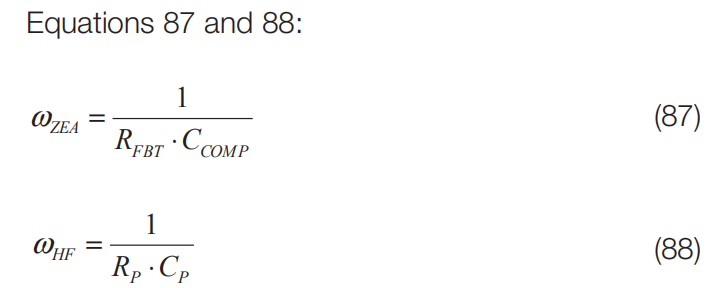

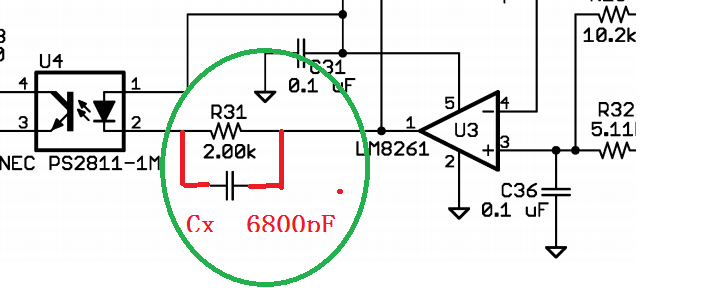

Usually, the controller will input the voltage signal into the COMP terminal, and the resistor Rp will be connected in series on the transistor side of the optocoupler, so that the pole of the optocoupler can be calculated according to the formula 88. The LM5035 is the current signal into the COMP terminal, the circuit diagram is as follows:

As shown above, I can see that the Cp capacitor is C33, but I don't know what the Rp resistor is.

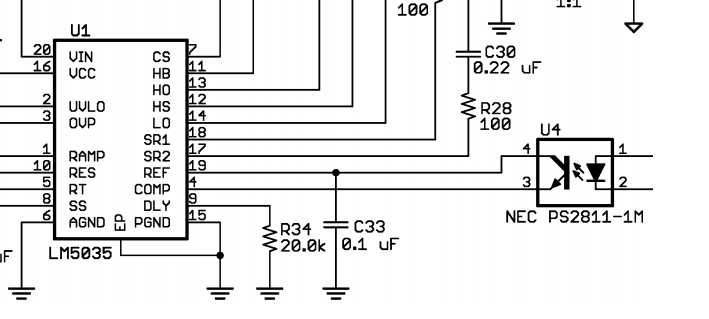

I saw the internal circuit diagram of the LM5035 chip, as follows:

Is that Rp a 5k resistor inside the LM5035?

I don't really believe that Rp will be the 5k resistor, because if Rp is a 5k resistor, the pole of the optocoupler is fz=1/(2*pi*C33*Rp)=1/(2*pi*0.1uF *5k)=318Hz, the frequency of this pole is too low, and the optocoupler pole is usually at 10kHz, so I am confused, what is the Rp value, how to measure or calculate?

I have another problem. When debugging, I connected a 6800pF capacitor Cx in parallel with the resistor R31 on the optocoupler diode side. This capacitor Cx is good for loop stability. But I don't know how to build this Cx equivalent model.

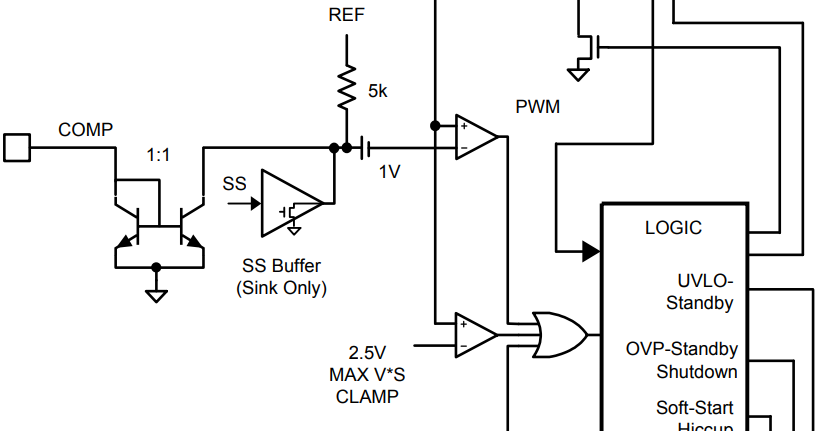

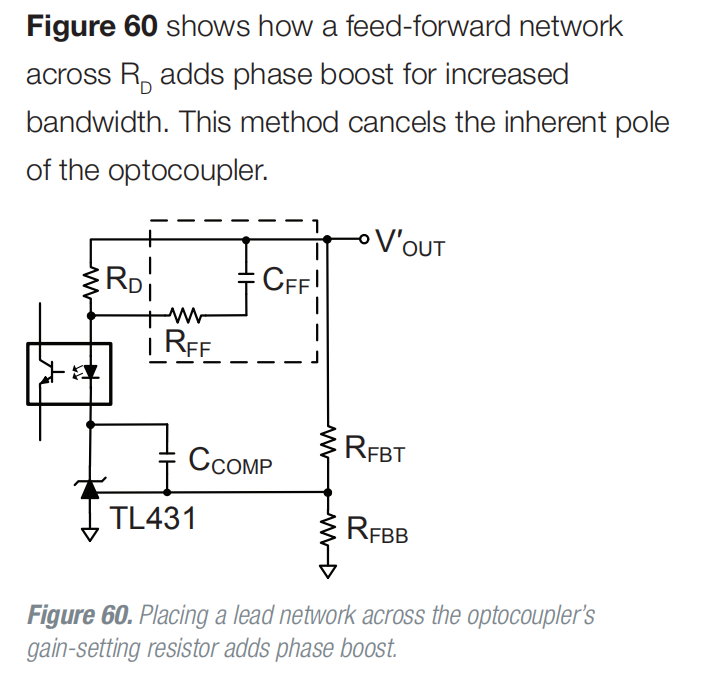

The 60th picture of Robert Sheehan and Louis Diana's application note describes a similar circuit that says it can offset the poles produced by the optocoupler, as shown below:

I think the Cx I added should have a zero effect, which improves the phase margin, so the system stability will be better.

However, I will not mathematically model Cx. I don't know how to calculate the frequency position of the zero point brought by Cx.

I look forward to your help, thank you!