Hello!

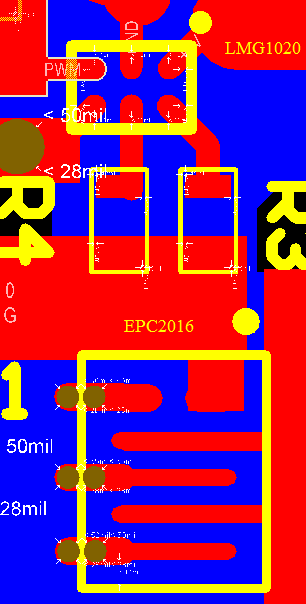

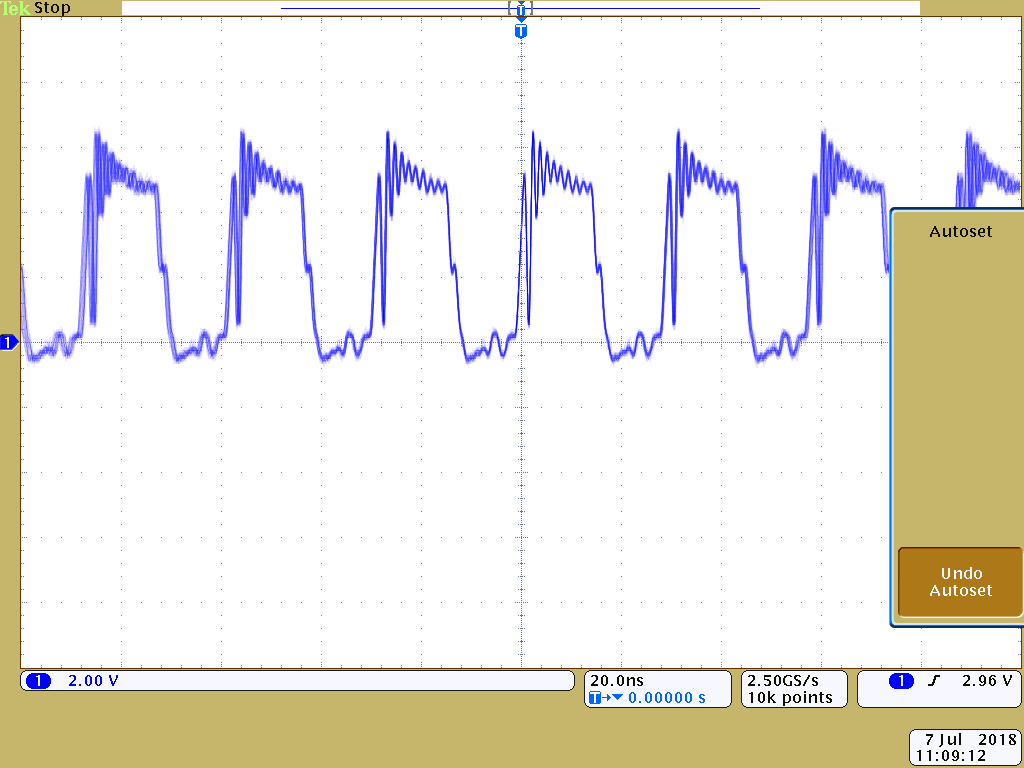

I use LMG1020 to design boost circuit. The Miller effect on the rising edge is very prominent. Can you give me some advice on how to improve the rising and falling edge waveform? The figures below show the layout and waveform of my circuit. The input signal is a square wave of 50% .

Looking forward to your reply. Thank you!