Hello Team,

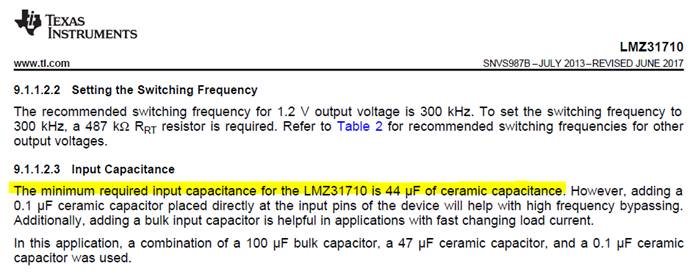

I am wondering if i can get some clarification on the Cin requirement for the LMZ31710.

Is the 44uF to mean the minimum after DC bias, tolerance, and temperature effects have been applied, i.e., worst case minimum? Or should I just read it as, “Use at least two 22uF, 1210, 25V.”

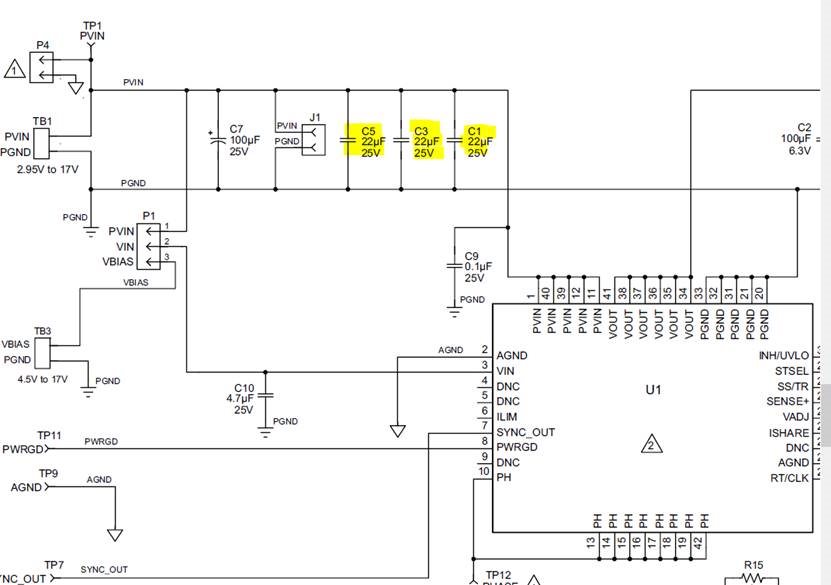

When I looked at the eval board schematic 3x22uF are used, which appears to meet the 44uF requirement on the surface.

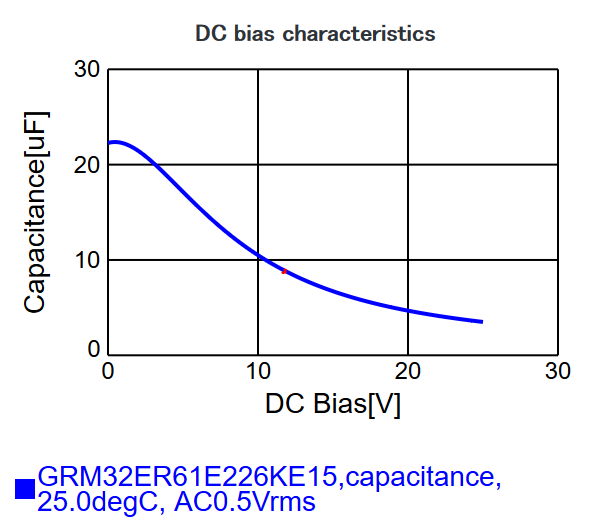

However, at 12V the 22uF caps reduce down to 9uF each from Murata’s data (see below). That’s 27uF total not including temperature and tolerance effects, so it is well below 44uF.

So what do I really need as a minimum Cin? Is the minimum capacitance of 44uF, if only ceramics are used? If I use a bulk cap (non-ceramic) in parallel does that relax the 44uF requirement? Note 7 seems to imply 44uF is still needed but the eval board seems to support that it is not.

This is critical for my customer as they are in a VERY area/volume constrained application, and do not wish to over-design needlessly.