Dear TI team,

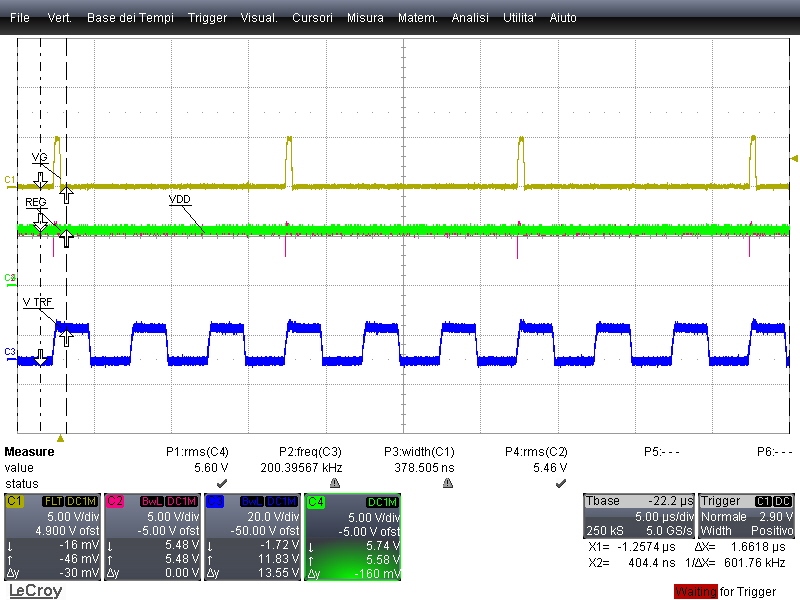

I tried to use the UCC24612 in a current doubler synchronous rectifer topology, but it doesn't work.

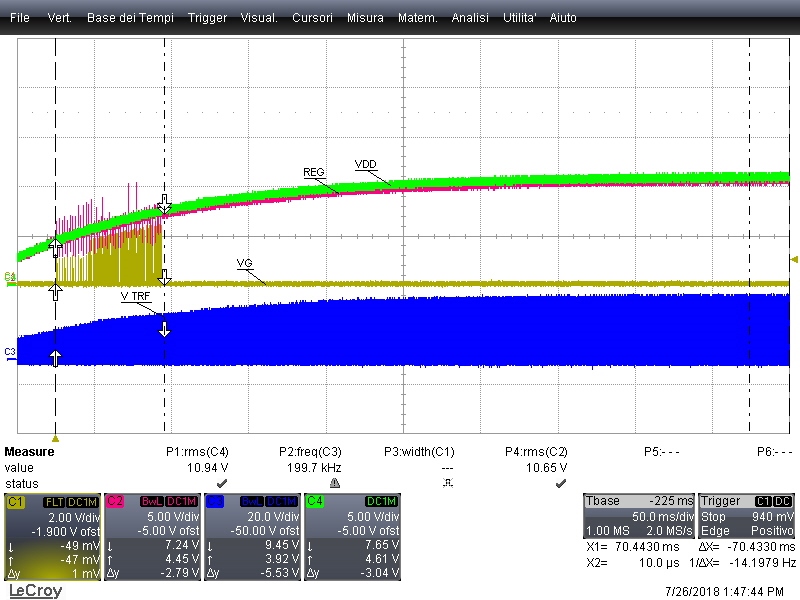

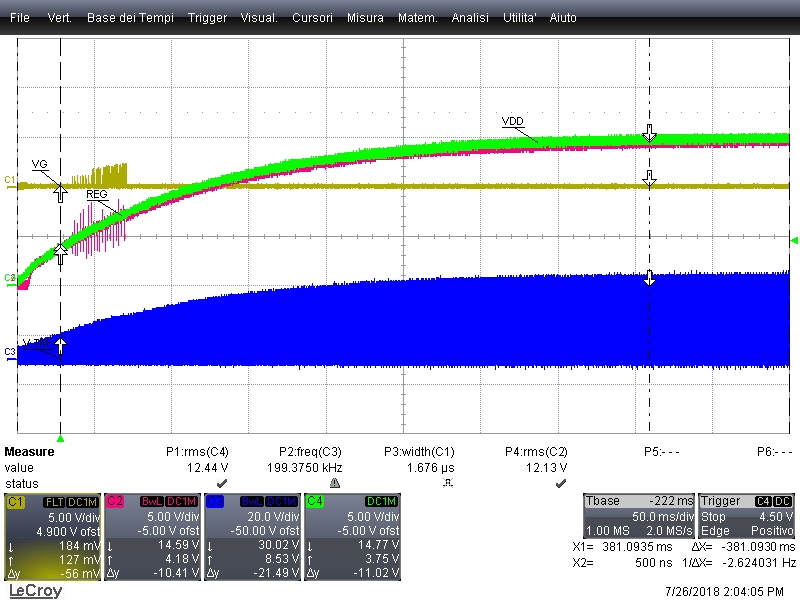

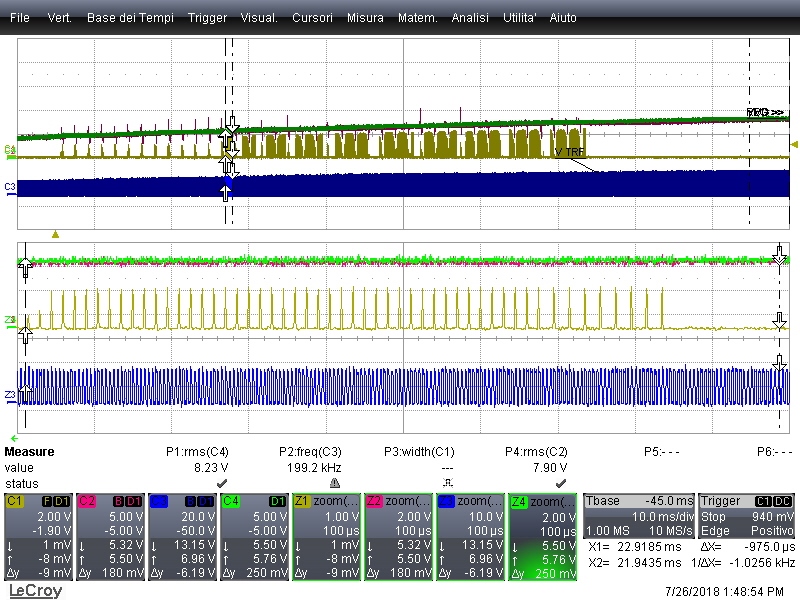

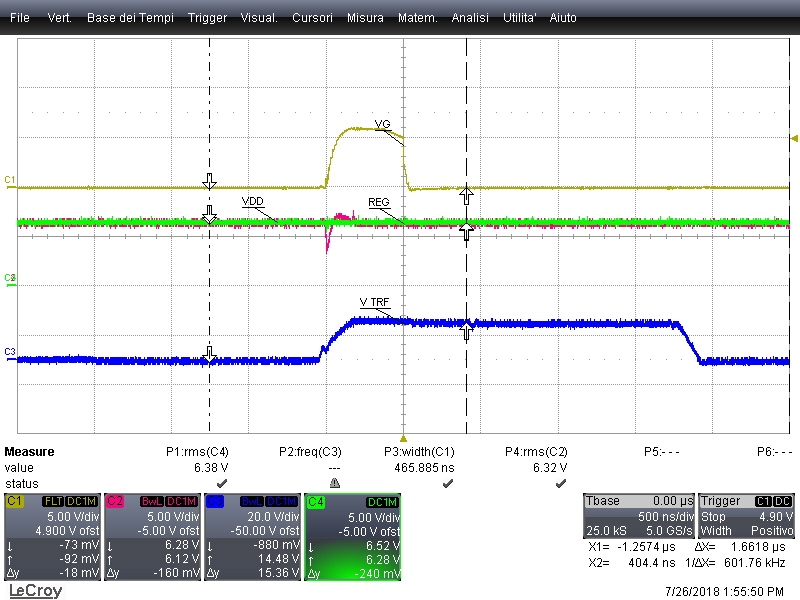

It seems to start producing gate pulses for a limited time interval at startup ramp, when the output voltage exceeds the 4.5V as stated in the datsheet.

Some milliseconds after no more gate commands are provided to mosfets.

Is it related to the rectifier topology?

Could it work in a full wave rectifier topology?