Dear All:

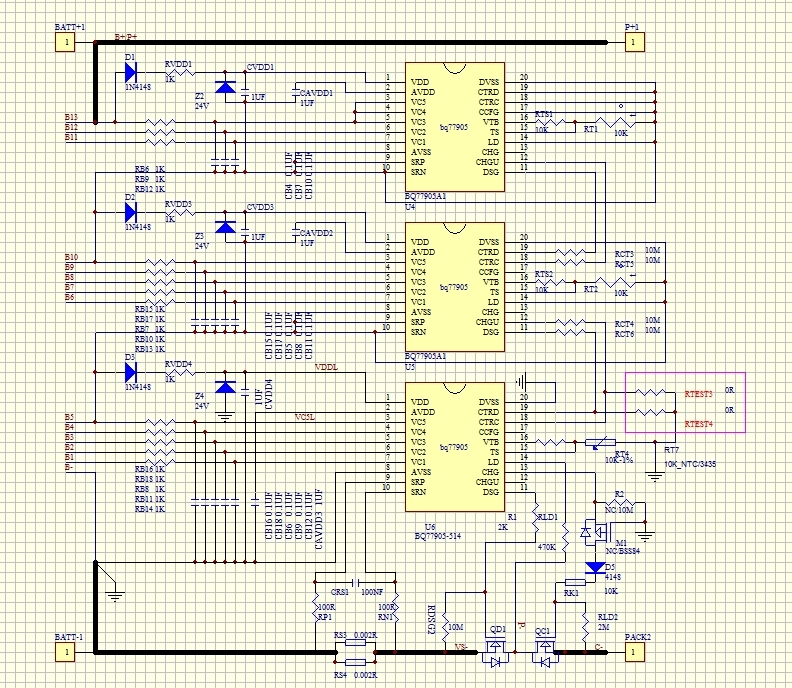

BQ77905 13S Application,I have add a diode(D1,D2,D3)in the VDD,the 13S SCH is

Do OCD2 test is abnormal.the DSG output gets oscillated before it gets locked.

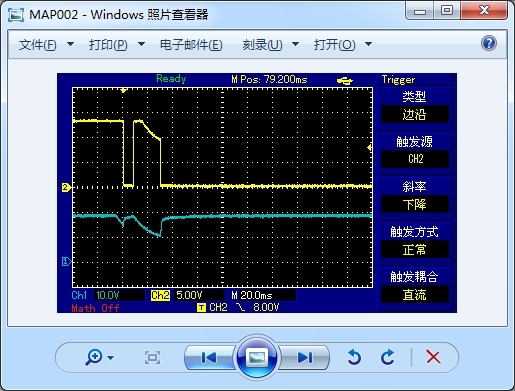

the PACK+(CH1),DSG(CH2) waveform is

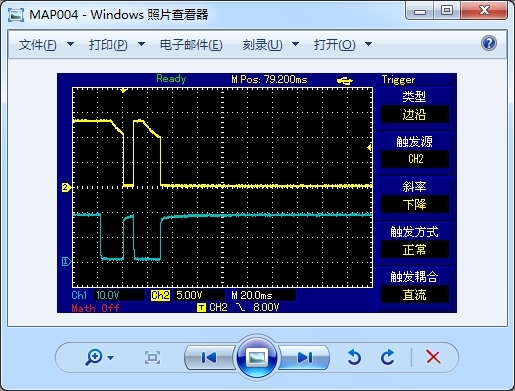

the VDD(CH1), DSG(CH2)Waveform is

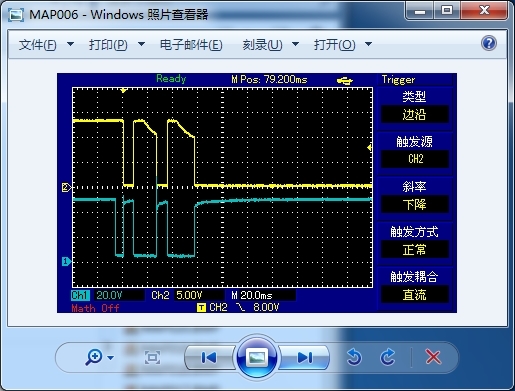

the VC5(CH1),DSG(CH2) waveform is

Why 13S Application OCD2 test DSG output Sometimes gets oscillated before it gets locked,please help explain the reason and give suggestions for improvement. Thank you.