Hi,

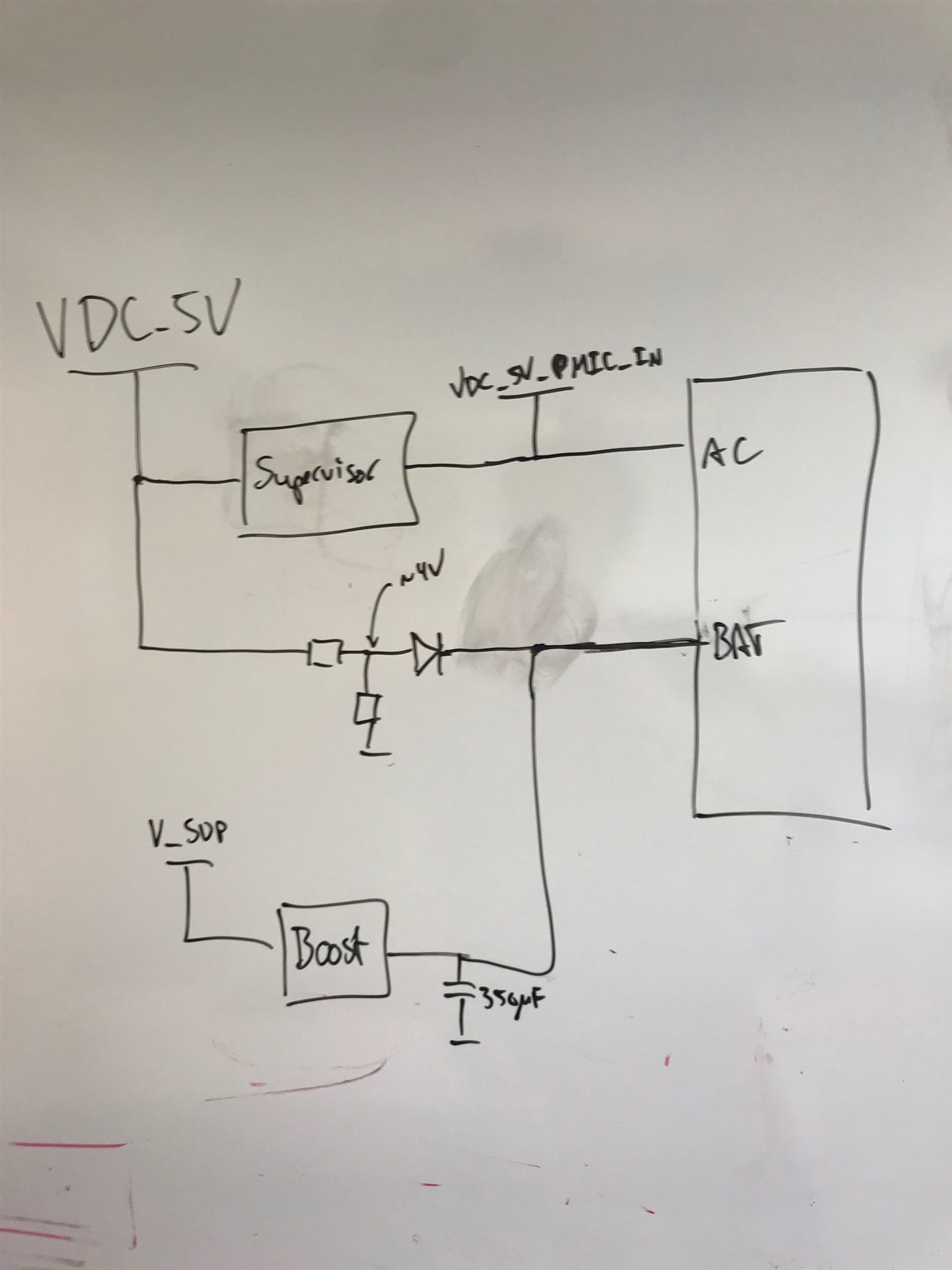

I have designed a board with BBB as a reference design with some additional circuitry around. I am using the TPS65217C with the Solution Circuit Number 3 mentioned in slva901 to avoid lock-up due to input brown-out events. See snip from the schematic below. In additon, V_BAT is connected to the output of a boost converter (with 350uF output capacitance). This boost converter boost the voltage from a supercap up to 5V to provide UPS functionality for some 10s of seconds in case of input power-loss.

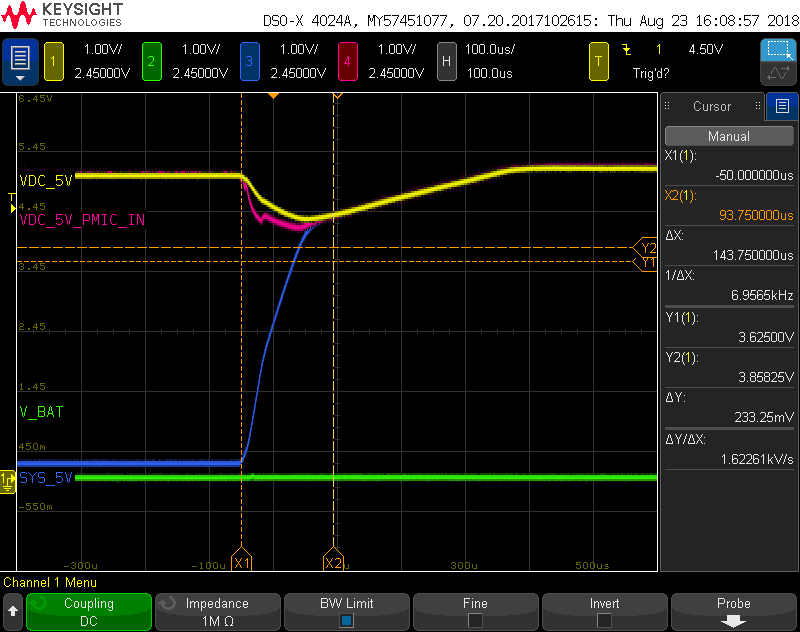

With the supercap discharged, which means that the boost converter connected to BAT is switched off and therefore no voltage applied to BAT pins, I see two different behaviours on power-up: either the board boots successfully after ~2 seconds (delay due to supervisor delay, see slva901), or the board needs an additional attempt (with another 2 seconds delay due to the supervisor) to successfully boot. A successful boot looks as shown below (Yellow trace: "VIN" from slva901, Pink trace: "VIN_PMIC" from slva901, blue trace: voltage on SYS pin, green trace: voltage on BAT pins).

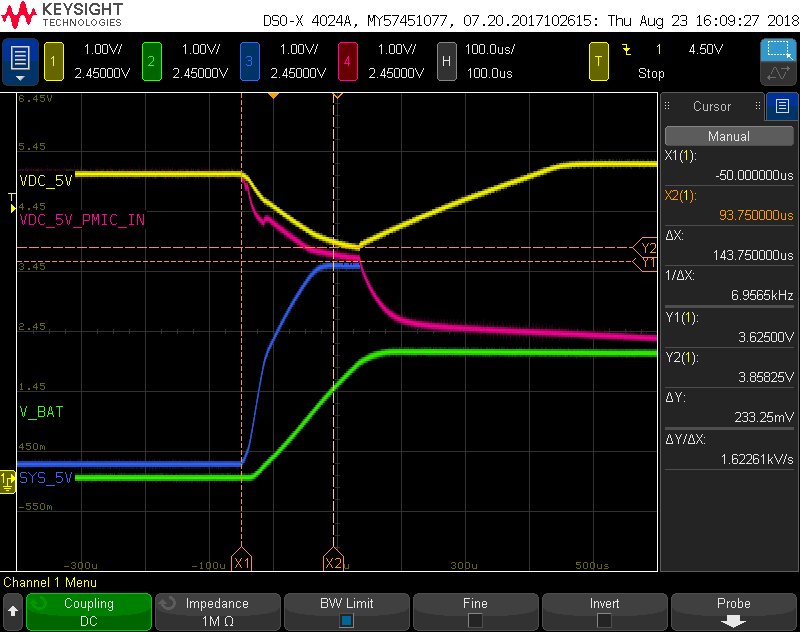

An unsuccessful boot is as shown below. The input voltage on the AC pin on the PMIC (pink trace) shuts down because the voltage VDC_5V dips below 4V which is detected by the supervisor, which in turn shuts down the voltage to the PMIC for another 2 seconds. After those 2 seconds, the board always boots successfully.

One major difference that can bee seen from the above plots is the voltage on the BAT pin when the SYS voltage is turned on by the PMIC. In the upper plot when the SYS voltage starts to increase the voltage on the BAT pins does not increase, but in the bottom plot the voltage on BAT increases significantly.

For me it seems that the PMIC sometimes during boot connects BAT to either AC or SYS, and sometimes it doesn't. When it does, the additional inrush current to the BAT pin causes the voltage on the input of the PMIC to drop much more, which causes the supervisor on the input of the PMIC to shut down the voltage to the PMIC for another 2 seconds.

Does anyone have any explanation to this? What I particularily don't understand is why the PMIC sometimes decides to charge the BAT pin and sometimes not.