Hi team,

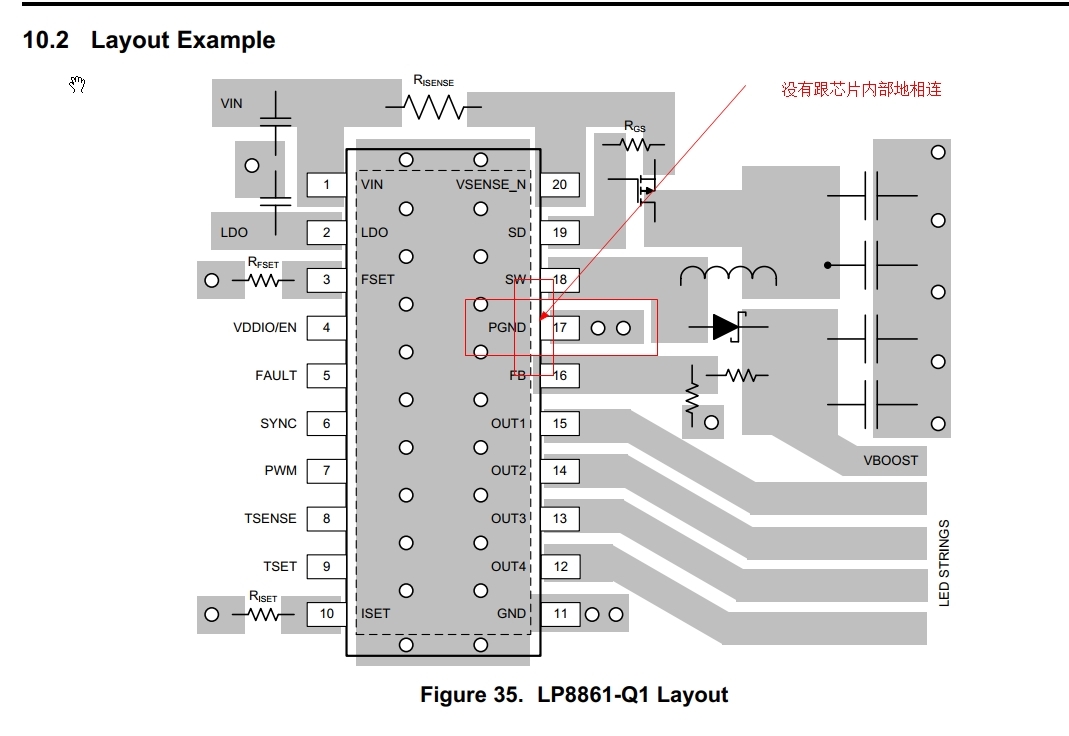

Could you check the recommendation for PGND connection? From the datasheet, it seems PGND is connected to GND through vias, can we connect PGND to GND directly from the top layer?

I checked the evm layout, the PGND is connected with SW. Is that correct?

Dongbao