Hi,

A question about VDDQ of TPS650942.

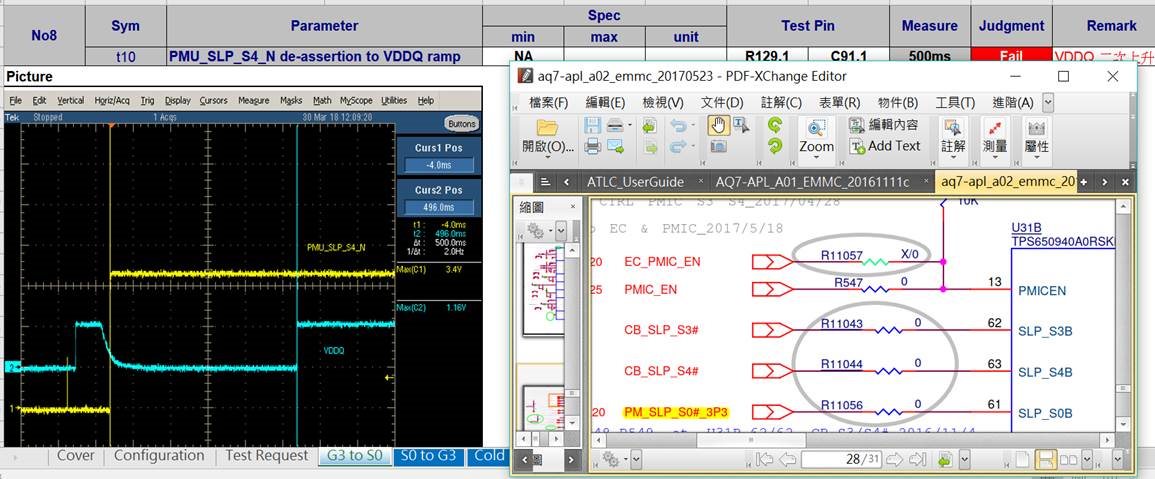

From G3 to S0 , we found VDDQ voltage has abnormal as picture 2.

The different between picture 1 and picture are S3 and S4 signal.

Picture 1, S3 and S4 from SOC to PMIC

Picture 2, S3 and S4 from SOC to EC to PMIC (abnormal).

I’d like to know which signal may cause VDDQ abnormal. (SLP_S4B or……..)

S3,S4 from SOC to PMIC control. It’s Normal

S3,S4 from SOC to EC to PMIC control . (VDDQ voltage has abnormal)

Please let me know if there are further information needed. Great thanks for your help.