Hello:

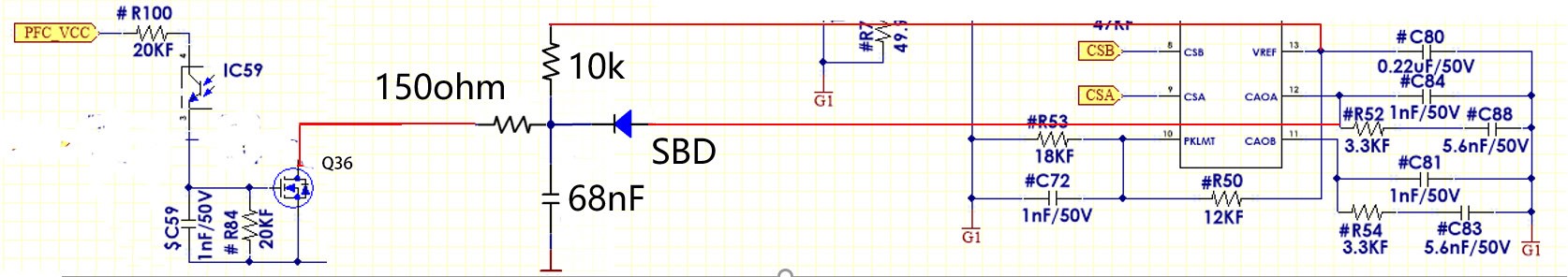

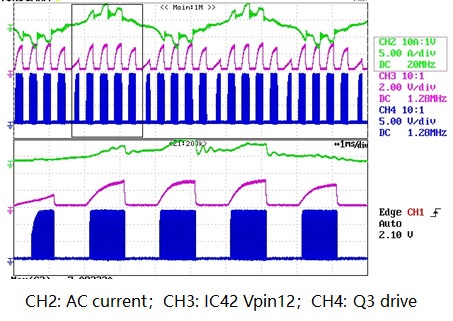

our customer has light load efficiency requirement. We have to turn off one phase at 10% load. In order to have " soft" enable one phase feature, we designed below circuit to turn on/off one of the phases.

IC59 is the photo coupler which will tranfer secondary light load detection signal to primary side.

During turn off: Q36 will be pulled low and CAOA will be pulled low by the SBD. Here we use schottky is because it has lower voltage drop than signal diode.

During turn on: 68nf cap will be charged by Vref via 10k resistor. And the CAOA will be clamped to 68nf cap voltage via SBD. So the voltage of CAOA is slowly rise up. In normal condition, CAOA is less than Vref. So SBD blocked CAOA to 68nf cap. This circuit will not impact PFC control loop in normal condition.

in that way, we can have soft start feature when two phase are enabled.

since it is a new circuit, our customer wants us to confirm it with TI FAE to avoid any side effect of this circuit.

please help to give your comment about that.

Thanks

Tao Wu