Hello

I am currently studying your UCD3138-based full-bridge hard-switch development board. I am learning how to set the PID coefficient.

I read your application note "UCD3138 Digital ControllerControl Theory" on page 30 to learn how to configure the poles of the PID.The manual tells me that the two zeros are configured: To boost the phase by 180o, a 2 pole 2 zero compensator is needed and should be located at 1/10 of fc.

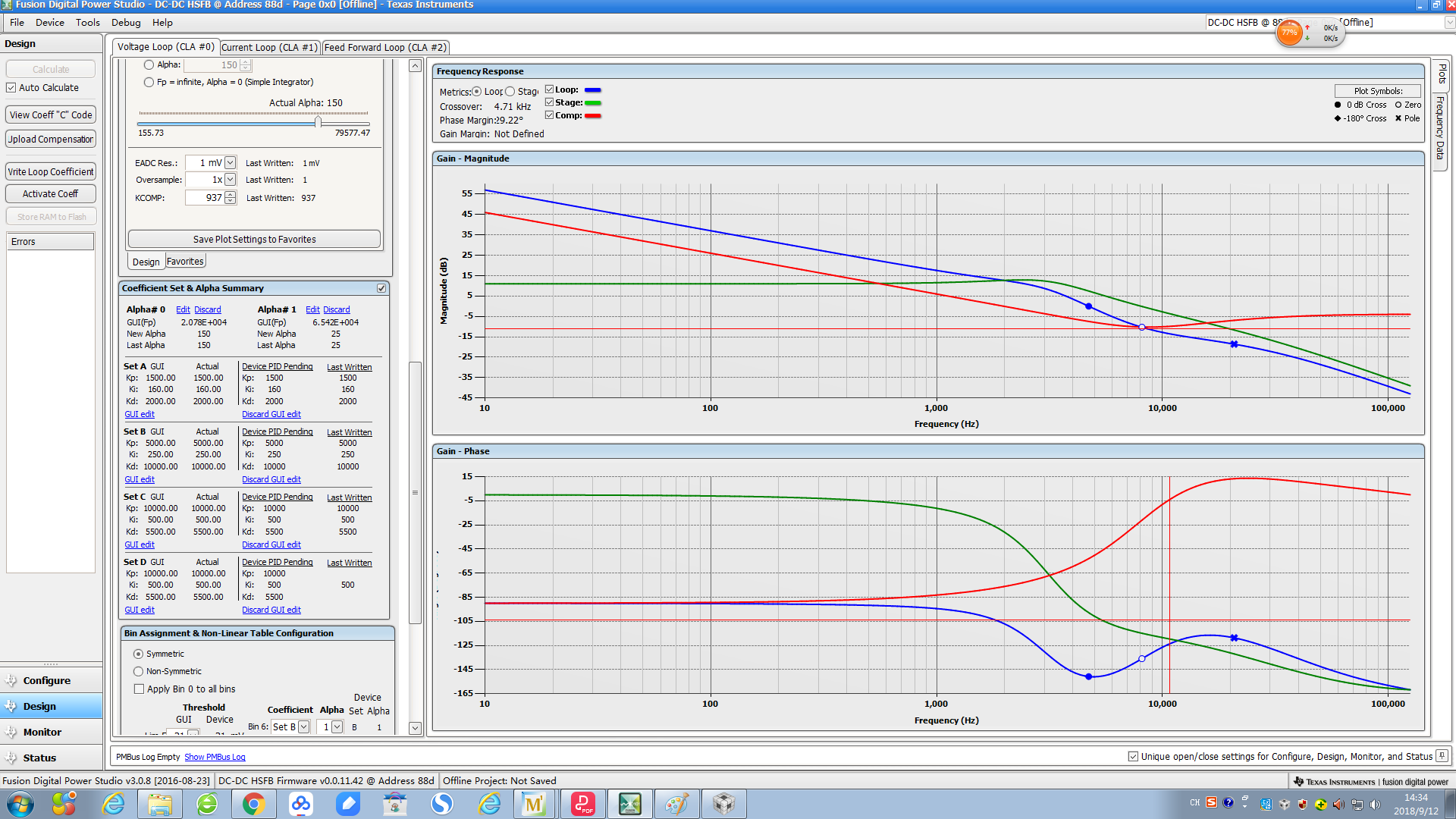

In the Fusion Design Offline software, I opened the bode simulation case of the UCD3138 full-bridge hard switch. As shown below:

The cross-over frequency of the system open-loop transfer function is approximately 4.7 kHz.

If the recommendations of the UCD3138 Digital Controller Control Theory are followed, the two zeros should be configured at 470 Hz, however, in practice, the two zeros are configured at approximately 8.1 kHz.

Why is this? What is the zero-point configuration principle of this full-bridge case?