Other Parts Discussed in Thread: CSD18535KCS, LM5101A

Dear sir,

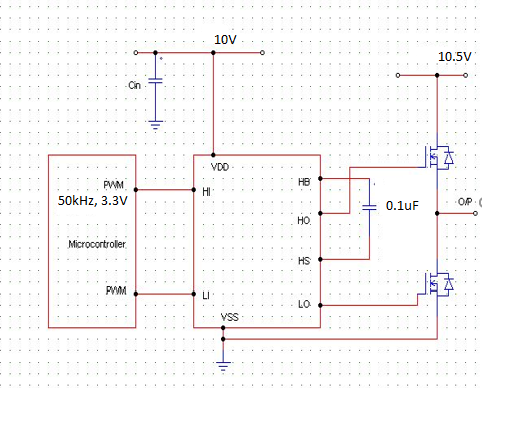

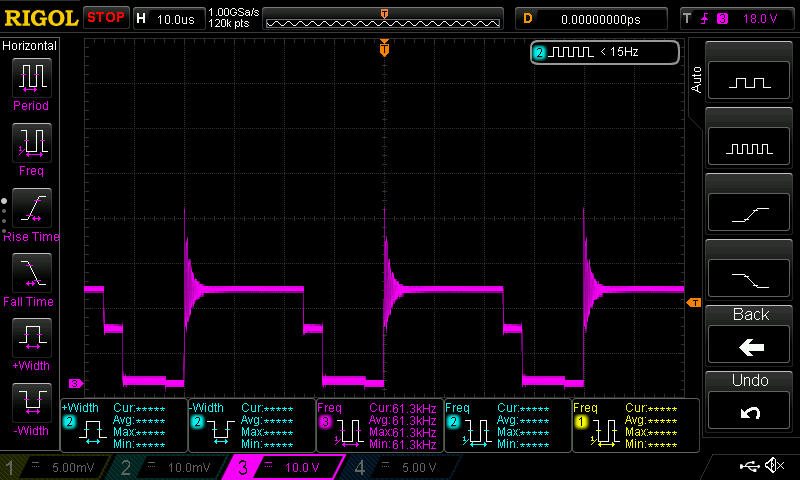

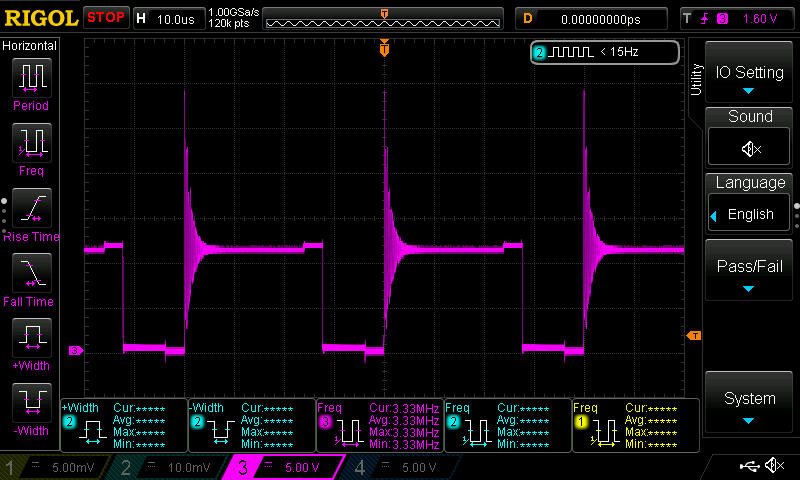

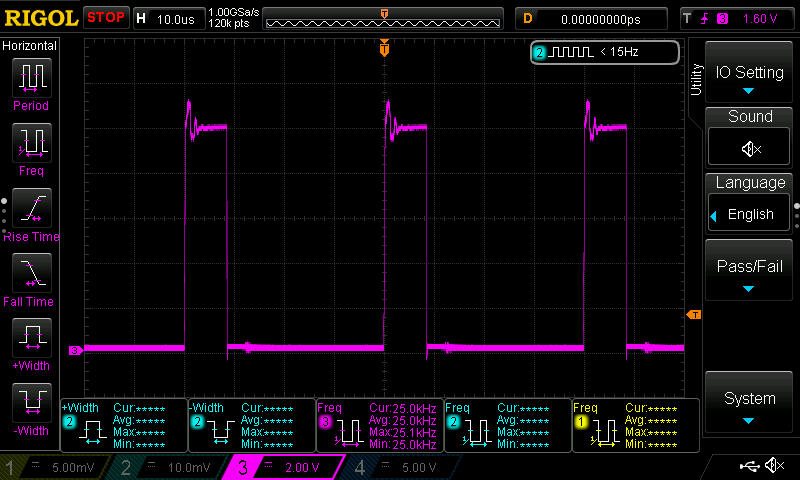

I have been using ucc27211 to drive High side mosfet. But I for not get the desired output. The output waveform was as shown in the diagram below. How can I reduce the ripple so as to get the desired ouput?